# LINEAR Integrated Circuits

SSD-202C 1975 DATABOOK Series

# A New Approach To Data Service . . . 1975 RCA Solid State DATABOOKS

Seven textbook-size volumes covering all current commercial RCA solid-state devices (through January 1, 1975)

| Linear Integrated Circuits and DMOS Devices (Data only) | .SSD-201C |

|---------------------------------------------------------|-----------|

| Linear Integrated Circuits and DMOS Devices             |           |

| (Application Notes only)                                | .SSD-202C |

| COS/MOS Digital Integrated Circuits                     | .SSD-203C |

| Power Transistors                                       | .SSD-204C |

| RF/Microwave Devices                                    | .SSD-205C |

| Thyristors, Rectifiers, and Diacs                       | .SSD-206C |

| High-Reliability Devices                                | .SSD-207C |

Announcement Newsletter: "What's New in Solid State"

Available FREE to all DATABOOK users.

"Bingo-type Response-Card Service" included with Newsletter Available FREE to all DATABOOK users.

Update Mailing Service available by subscription.

Indexed Binder available for Update Filing.

NOTE: See pages 3 and 4 for additional information on this total data service. To qualify for Newsletter mailing, use the form on page 4 (unless you received your DATABOOK directly from RCA). You must qualify annually since a new mailing list is started for each edition of the DATABOOKS.

# RC/I LINEAR Integrate

This DATABOOK contains application notes on linear integrated circuits and DMOS (discrete MOS field-effect) devices presently available from RCA Solid State Division as standard products. Data sheets on both linear IC's and DMOS devices are contained in a separate DATABOOK, SSD-201C.

For ease of reference, the application notes in this book are arranged in numerical sequence. The index on pages 6-8 groups the notes in the same categories used in the SSD-201C selection charts: (a) operational amplifiers; (b) arrays; (c) differential and broadband (video) amplifiers; (d) power-control, computer-interface, and analog-multiplier circuits; (e) consumer circuits; (f) DMOS devices.

Trade Mark(s) Registered ® Marca(s) Registrada(s)

Copyright 1974 by RCA Corporation (All rights reserved under Pan-American Copyright Convention)

Printed in USA/11-74

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RCA.

RCA Solid State | Box 3200 | Somerville, N.J., U.S.A. 08876 RCA Limited | Sunbury-on-Thames | Middlesex TW16 7HW, England RCA s.a. | 4400 Herstal | Liege, Belgium

# RCA Solid State Total Data Service System

The RCA Solid State DATABOOKS are supplemented throughout the year by a comprehensive data service system that keeps you aware of all new device announcements and lets you obtain as much or as little product information as you need — when you need it.

New solid-state devices and related publications announced during the year are described in a newsletter entitled "What's New in Solid State". If you obtained your DATABOOK(s) directly from RCA, your name is already on the mailing list for this newsletter. If you obtained your book(s) from a source other than RCA and wish to receive the newsletter, please fill out the form on page 4, detach it, and mail it to RCA.

Each newsletter issue contains a "bingo"-type fast-response form for your use in requesting information on new devices of interest to you. If you wish to receive all new product information published throughout the year, without having to use the newsletter response form, you may subscribe to a mailing service which will bring you all new data sheets and application notes in a package every other month. You can also obtain a binder for easy filing of all your supplementary material. Provisions for obtaining information on the update mailing service and the binder are included in the order form on page 4.

Because we are interested in your reaction to this approach to data service, we invite you to add your comments to the form when you return it, or to send your remarks to one of the addresses listed at the top of the form. We solicit your constructive criticism to help us improve our service to you.

# Order Form for "What's New in Solid State" and for further information on Update Mailings and Binders

Please fill out just one copy of this form, and mail it to: (a) from U.S.A. and Canada: RCA Solid State Division Box 3200 Somerville, N. J., U.S.A. 08876 (b) from Latin America and Far East: **RCA Solid State** International Sales Somerville, N. J., U.S.A. 08876 (c) from United Kingdom, Europe, Middle East, and Africa: RCA Limited RCA s.a. Sunbury-on-Thames or 4400 Herstal Middlesex TW16 7HW, England Liege, Belgium ☐ Please add my name to the mailing list for "What's New in Solid State" Please send me details on obtaining update mailings for my DATABOOKS and a binder for filing of supplementary material. Name (Last) (Initials) Compan Address (Street, RFD, P.O. Box) (Number) Home **Business** (City) (State or Prov.) (Country) (Zip or Pstl. Zone) Product Interest: Activity: (Check One) Function: (Check One) (Indicate order of interest if more than one is marked) A

Executive/Administration A □ Broadcast B

Communication B

Purchasing/Procurement A Linear IC's C | Instrumentation/Control C

Research/Development B Digital IC's, COS/MOS D

Computer/Data Processing D Design Engineer E Computer, Peripheral E | Application/Components C Digital IC's, Bipolar F

Automotive Engineer D Thyristors/Rectifiers G | Industrial F

Production/Manufacturing H

Medical E Liquid Crystals G □ Documentation/Library I □ Research H D Reliability/QA F Semiconductor Diodes □ Transportation I □ Education/Training K

Consumer, Electronic G RF Power Semiconductors J

Program/Project Management L

Consumer, Appliance K □ Marketing MOSFETS M □ Space N □ Ordnance

O

Avionics

P

Electronic Warfare

I Power Transistors

J Power Hybrid Circuits

# **Table of Contents**

|                                                      | Page |

|------------------------------------------------------|------|

| Index to Application Notes                           | . 6  |

| Operating Considerations for RCA Solid State Devices | . 9  |

| Application Notes on Linear IC's and DMOS Devices    | . 14 |

| Subject Index                                        | .442 |

# **Index to Application Notes**

| on Linear IC Operati  | onal Amplifiers                                                                                          | age |

|-----------------------|----------------------------------------------------------------------------------------------------------|-----|

| ICAN-5015             | "Application of the RCA-CA3008 and CA3010 Integrated-Circuit Operational Amplifiers"                     | 87  |

| ICAN-5213             | "Application of the RCA-CA3015 and CA3016 Integrated-Circuit Operational Amplifiers"                     |     |

| ICAN-5290             | "Intergrated-Circuit Operational Amplifiers"                                                             |     |

| ICAN-5641             | "Application of RCA-CA3033 and CA3033A High-<br>Performance Integrated-Circuit Operational<br>Amplifiers |     |

| ICAN-6668             | "Applications of the CA3080 and CA3080A High-<br>Performance Operational Transconductance<br>Amplifiers" |     |

| ICAN-6732             | "Measurement of Burst ("Popcorn") Noise in Linear Integrated Circuits"                                   |     |

| on Linear IC Arrays   |                                                                                                          |     |

| ICAN-4072             | "Applications of the RCA-CA3048 Integrated-Circuit Amplifier Array"                                      | 49  |

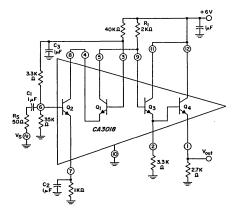

| ICAN-5296             | "Application of the RCA-CA3018 Integrated-Circuit Transistor Array"                                      | 93  |

| ICAN-5299             | "Application of the RCA-CA3019 Integrated-Circuit Diode Array"                                           | 98  |

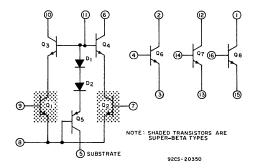

| ICAN-6222             | "Designing with an IC Transistor Array Containing Matched Super-Beta Transistors" (CA3095E)33            | 31  |

| on Linear IC Differer | ntial and Broadband (Video) Amplifiers                                                                   |     |

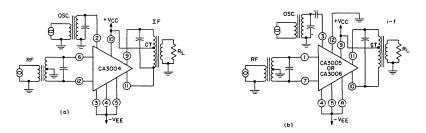

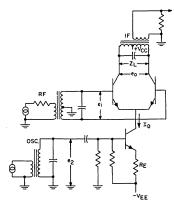

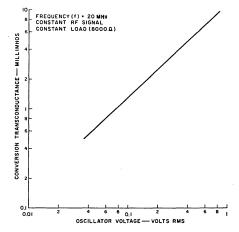

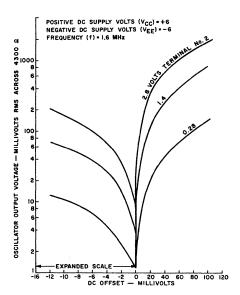

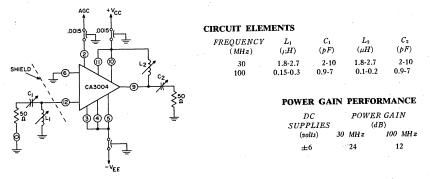

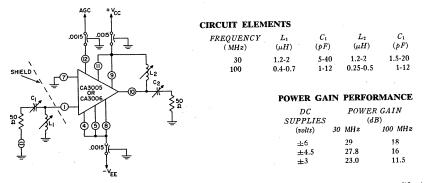

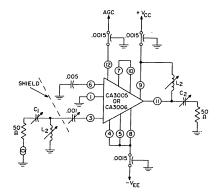

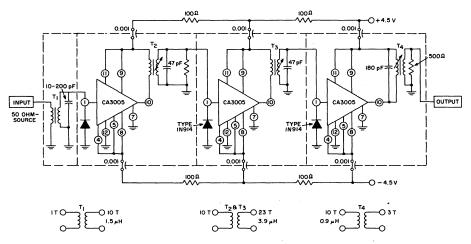

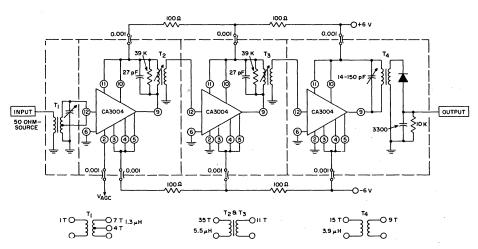

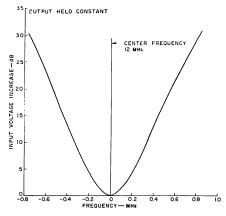

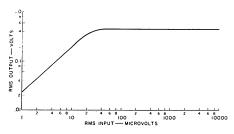

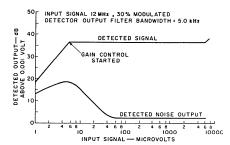

| ICAN-5022             | "Application of the RCA-CA3004, CA3005, and CA3006 Integrated-Circuit RF Amplifiers"                     | 02  |

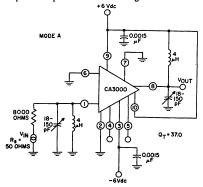

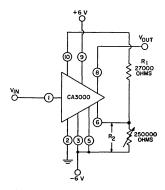

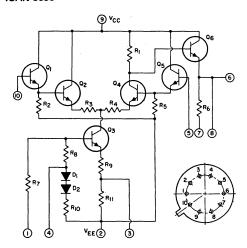

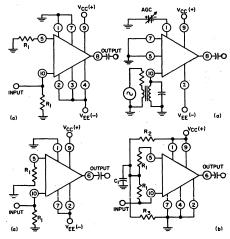

| ICAN-5030             | "Application of the RCA-CA3000 Integrated-Circuit DC Amplifier"                                          |     |

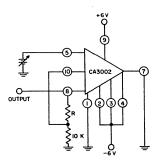

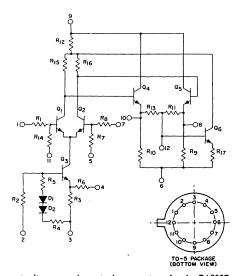

| ICAN-5036             | "Application of the RCA-CA3002 Integrated-Circuit IF Amplifer"                                           | 39  |

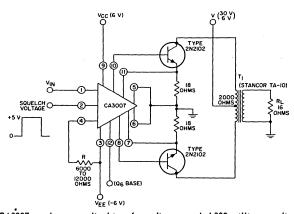

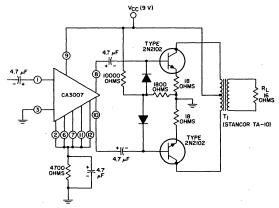

| ICAN-5037             | "Application of the RCA-CA3007 Integrated-Circuit Audio Amplifier"                                       | 48  |

| ICAN-5038             | "Application of the RCA-CA3001 Integrated-Circuit Video Amplifier"                                       |     |

| ICAN-5337             | "Application of the RCA-CA3028A and CA3028B Integrated-Circuit RF Amplifiers in the HF and VHF Ranges"   | 04  |

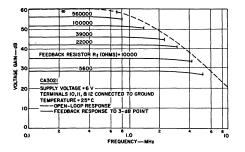

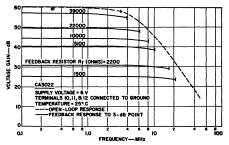

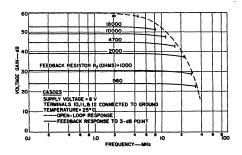

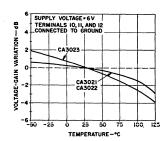

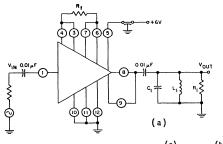

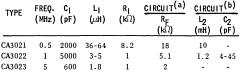

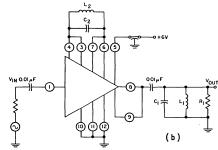

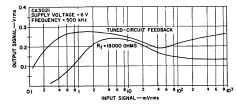

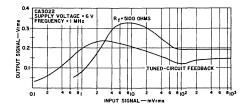

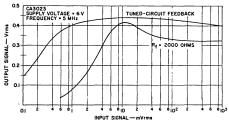

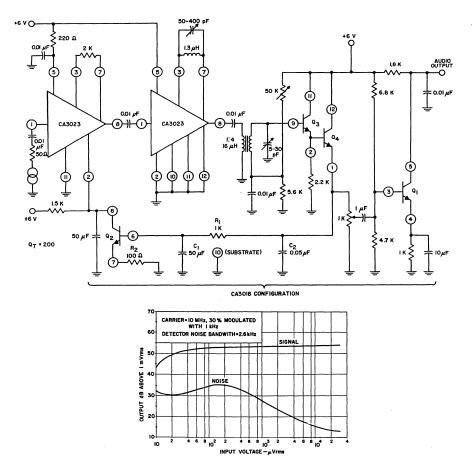

| ICAN-5338             | "Application of the RCA-CA3021, CA3022, and CA3023 Integrated-Circuit Wideband Amplifiers"               | 14  |

| ICAN-5766             | "Application of the RCA-CA3020 and CA3020A Integrated-Circuit Multi-Purpose Wide-Band Power Amplifiers"  |     |

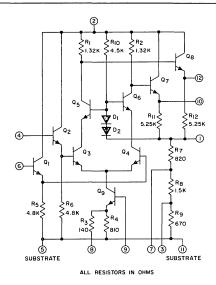

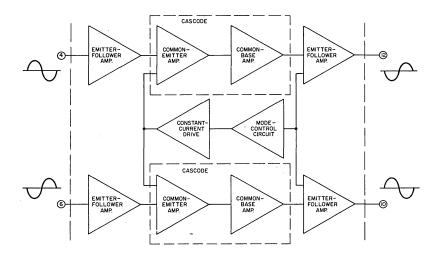

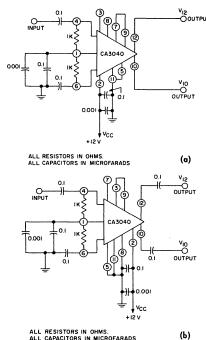

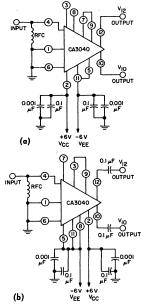

| ICAN-5977             | "Principal Features and Applications of the RCA-CA3040 Integrated-Circuit Wideband Amplifier"            | 60  |

# **Index to Application Notes**

| on Linear IC Power-0 | Control, Computer-Interface, and Analog-Multiplier Circuits                                                 | Page |

|----------------------|-------------------------------------------------------------------------------------------------------------|------|

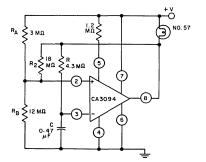

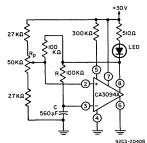

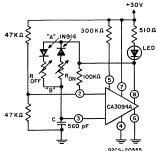

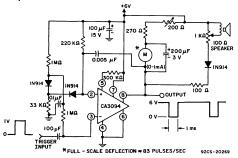

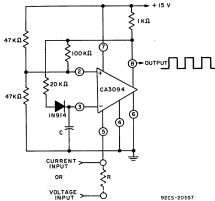

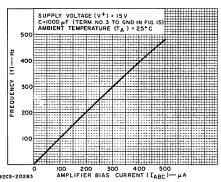

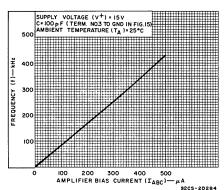

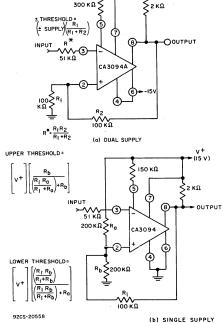

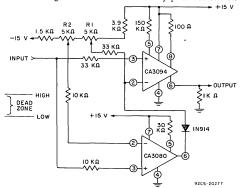

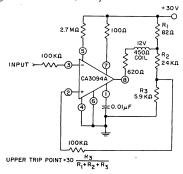

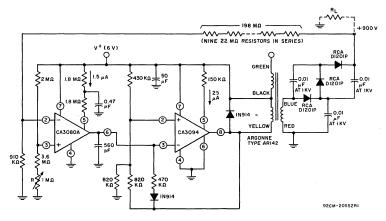

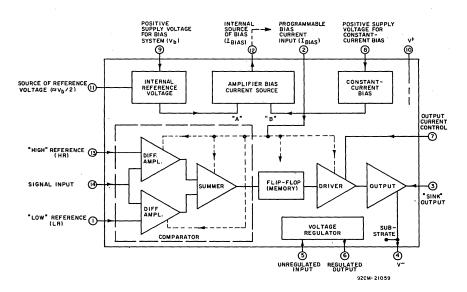

| ICAN-6048            | "Some Applications of a Programmable Power-<br>Switch/Amplifier IC" (CA3094T, CA3094AT,<br>CA3094BT)        | 275  |

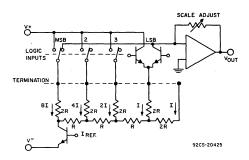

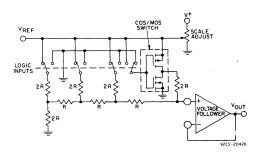

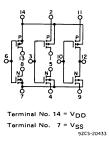

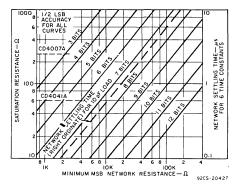

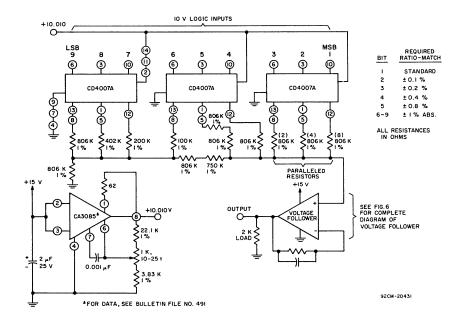

| ICAN-6080            | "Digital-to-Analog Conversion Using the RCA-CD4007A COS/MOS IC"                                             |      |

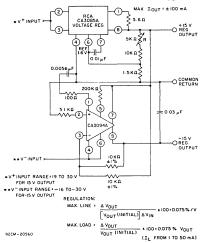

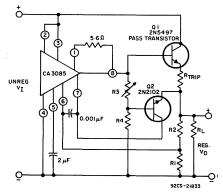

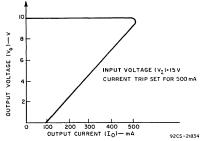

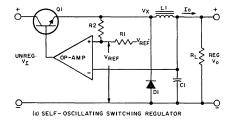

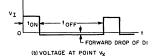

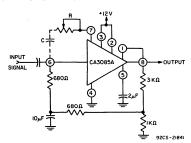

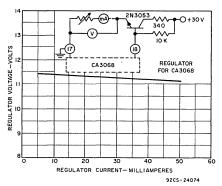

| ICAN-6157            | "Applications of the CA3085-Series Monolithic IC Voltage Regulators"                                        |      |

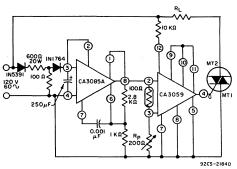

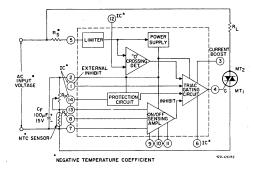

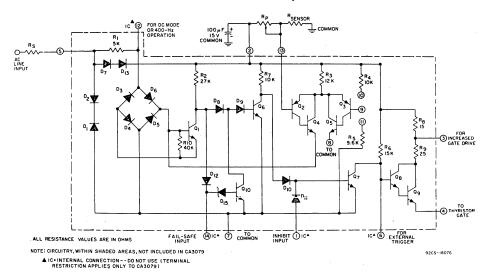

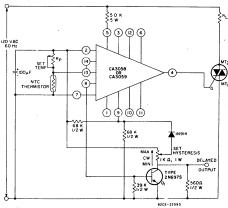

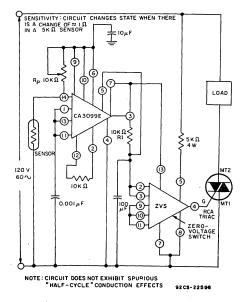

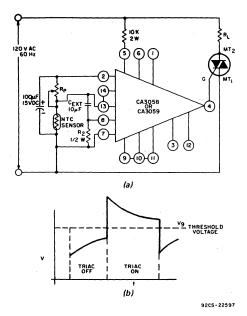

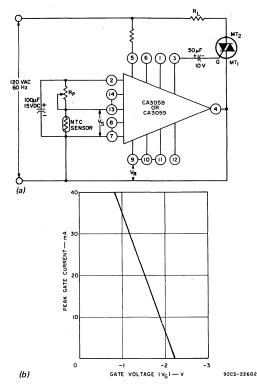

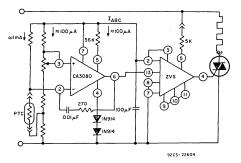

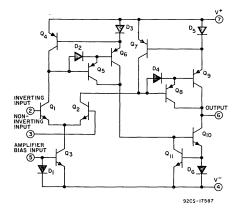

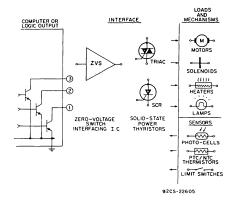

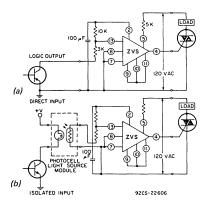

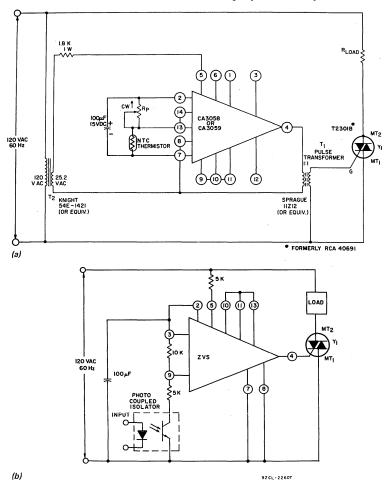

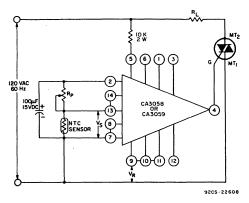

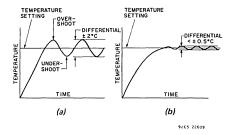

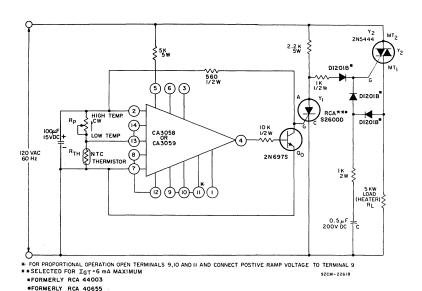

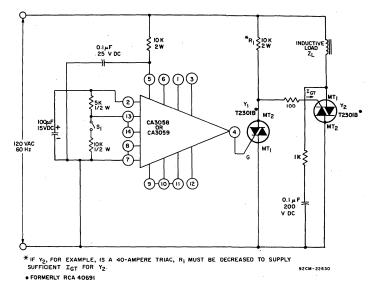

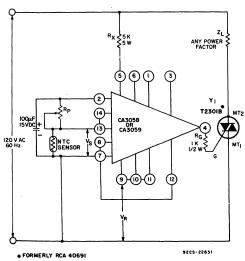

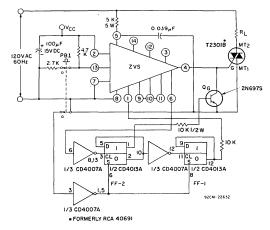

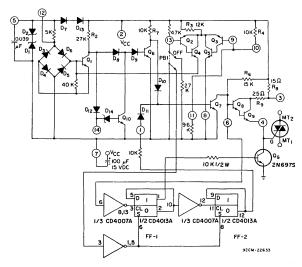

| ICAN-6182            | "Features and Applications of RCA Integrated-<br>Circuit Zero-Voltage Switches" (CA3058,<br>CA3059, CA3079) |      |

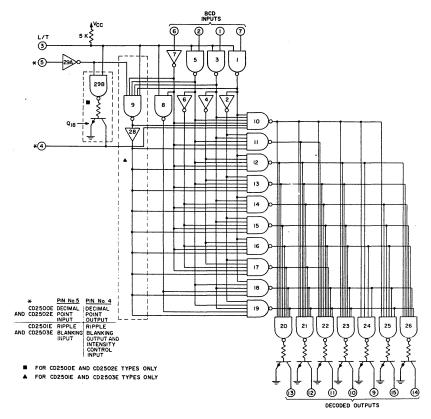

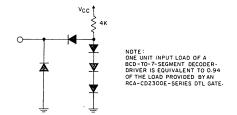

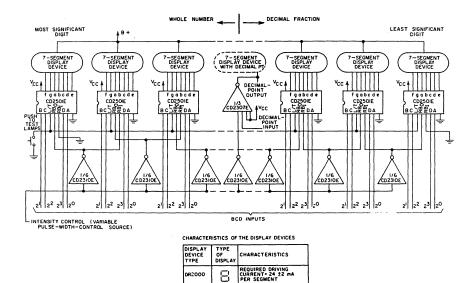

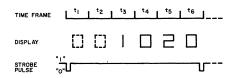

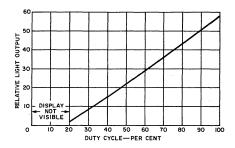

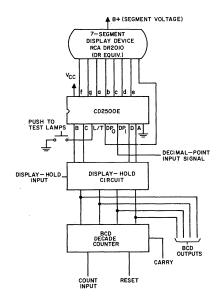

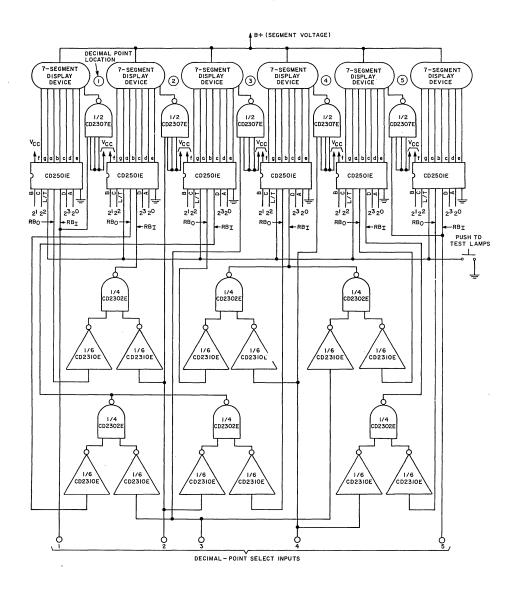

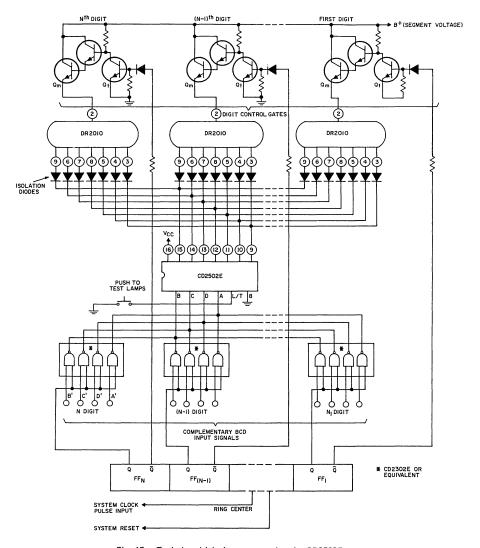

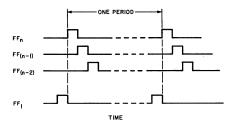

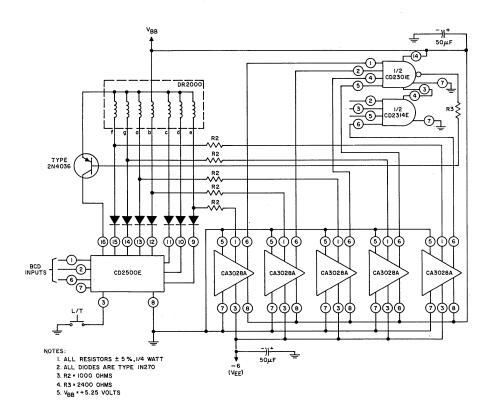

| ICAN-6294            | "Features and Applications of RCA-CD2500E Series MSI BCD-to-7-Segment Decoder-Drivers"                      | 368  |

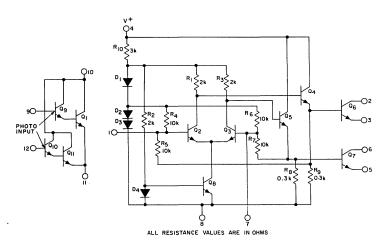

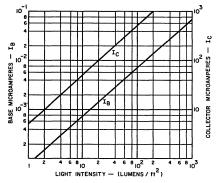

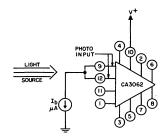

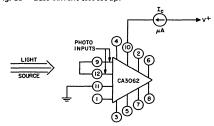

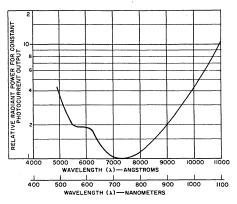

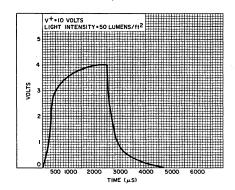

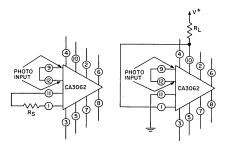

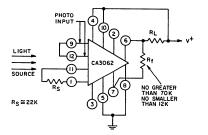

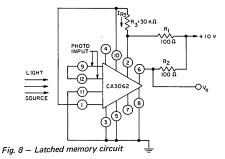

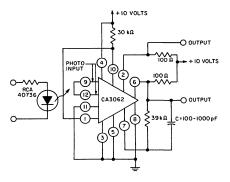

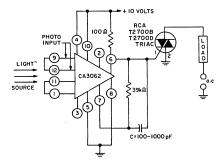

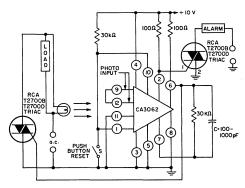

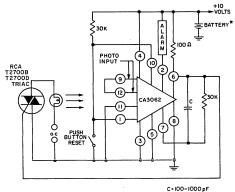

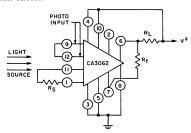

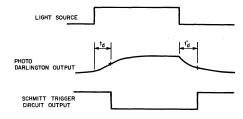

| ICAN-6538            | "Applications of the RCA-CA3062 IC Photo-<br>Detector and Power Amplifier in Switching<br>Circuits"         |      |

|                      |                                                                                                             |      |

| on Linear IC Consum  | er Circuits                                                                                                 |      |

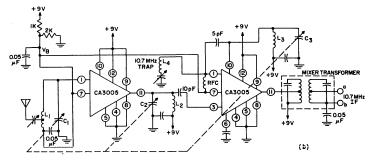

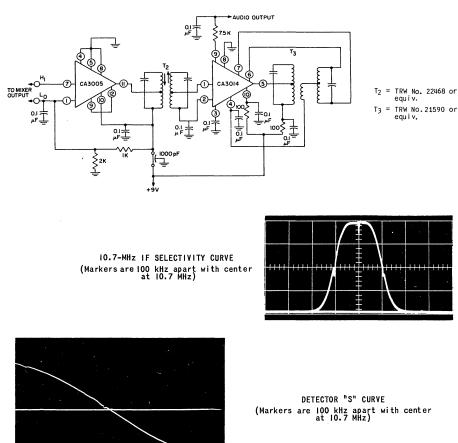

| ICAN-5269            | "Integrated Circuits for FM Broadcast Receivers"                                                            | 166  |

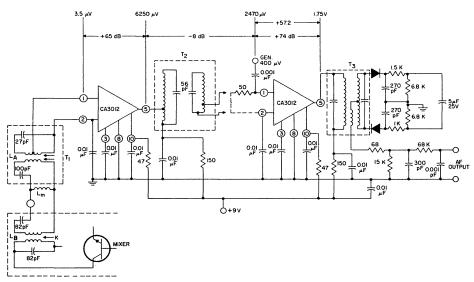

| ICAN-5380            | "Integrated-Circuit Frequency-Modulation IF Amplifiers"                                                     |      |

| ICAN-5831            | "Application of the RCA-CA3044 and CA3044VI Integrated Circuits in Automatic-Fine-Tuning Systems"           |      |

| ICAN-5841            | "Feedback-Type Volume-Control Circuits for RCA-CA3041 and CA3042 Integrated Circuits"                       | 256  |

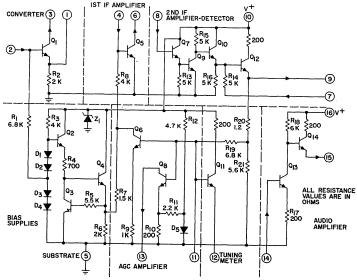

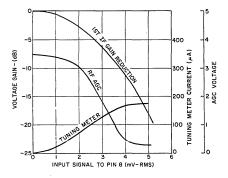

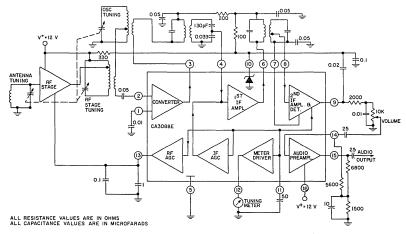

| ICAN-6022            | "An IC for AM Radio Applications" (CA3088E)                                                                 | .271 |

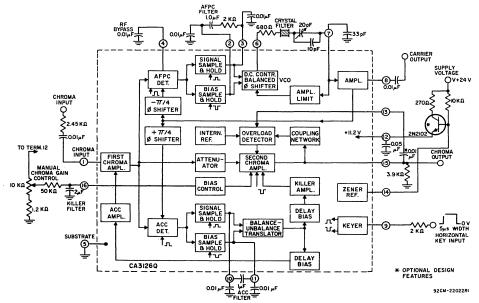

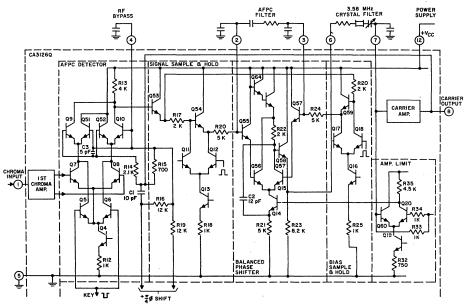

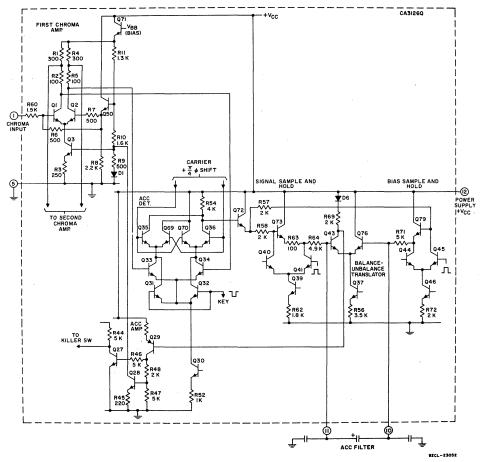

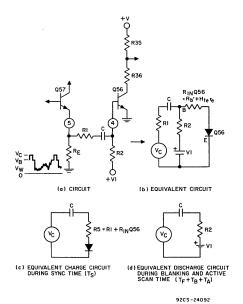

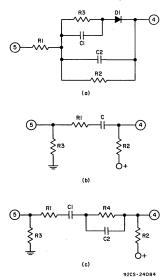

| ICAN-6247            | "Application of the CA3126Q Chroma-<br>Processing IC Using Sample-and-Hold<br>Circuit Techniques"           | .340 |

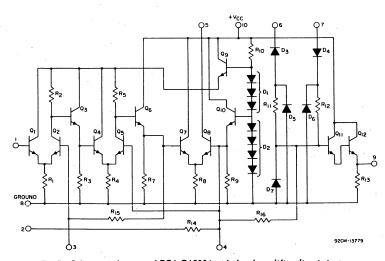

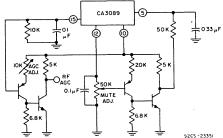

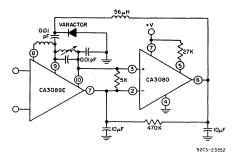

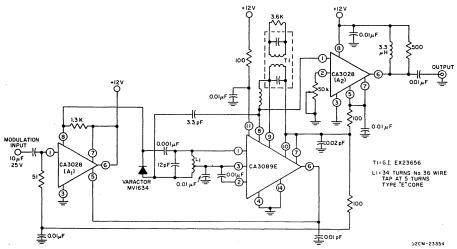

| ICAN-6257            | "Application of the CA3089E FM-IF Subsystem"                                                                |      |

| ICAN-6259            | "Integrated Circuit Stereo Decoder Using the CA3090Q Stereo Multiplex Demodulator"                          |      |

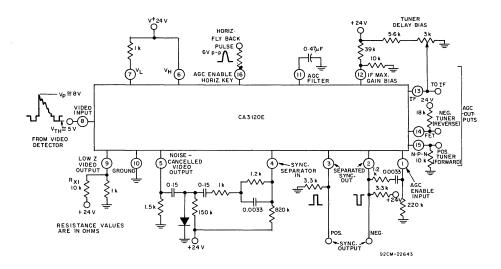

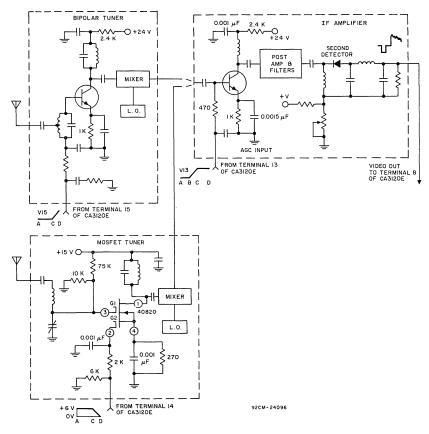

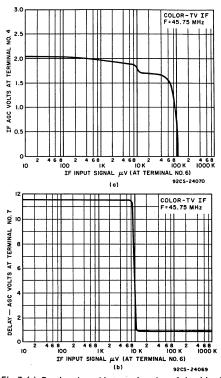

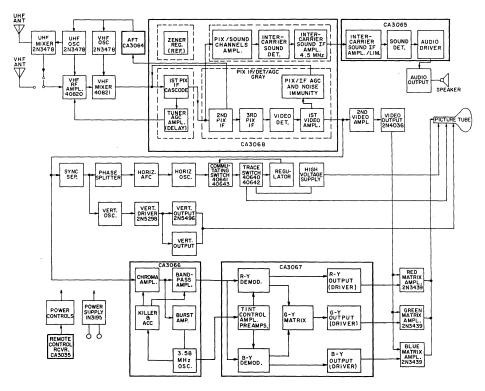

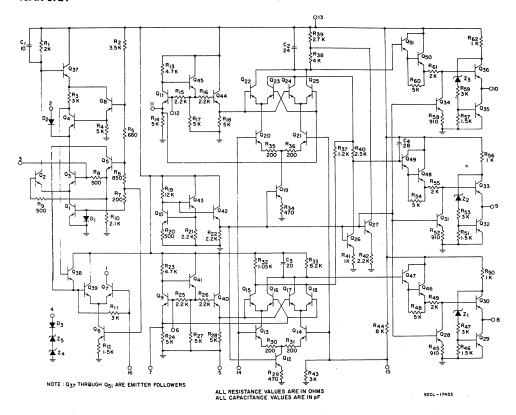

| ICAN-6302            | "Description and Application of RCA-CA3120E IC TV Signal Processor"                                         | .379 |

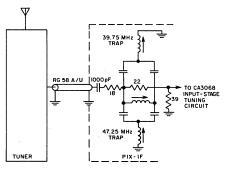

| ICAN-6303            | "A Single IC for the Complete PIX-IF System in TV Receivers" (CA3068)                                       | .388 |

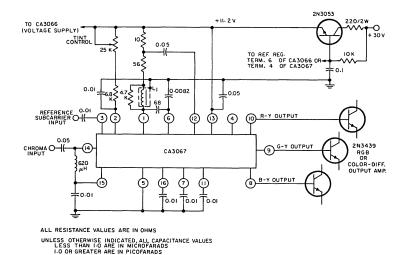

| ICAN-6724            | "A Flexible Integrated-Circuit Color Demodulator for Color Television" (CA3067)                             | .427 |

| on MOS/FET Devices   |                                                                                                             |      |

| AN-3193              | "Application Considerations for the RCA-3N128 VHF MOS Field-Effect Transistor"                              | 14   |

| AN-3341              | "VHF Mixer Design Using the RCA-3N128 MOS Transistor"                                                       |      |

# **Index to Application Notes**

| on MOS/FET Devices | (cont'd)                                                                                   | Page |

|--------------------|--------------------------------------------------------------------------------------------|------|

| AN-3452            | "Chopper Circuits Using RCA MOS Field-Effect Transistors"                                  | . 25 |

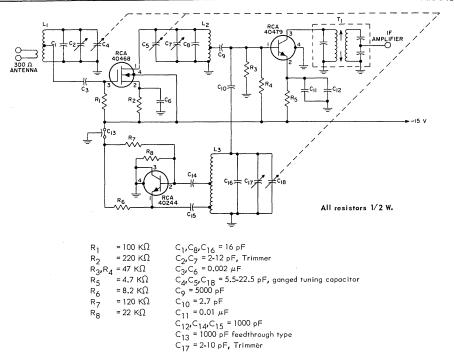

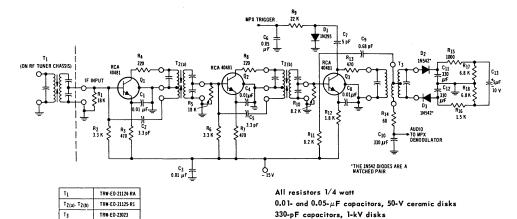

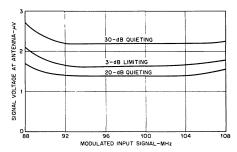

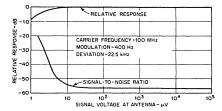

| AN-3453            | "An FM Tuner Using an RCA-40468 MOS-<br>Transistor RF Amplifier"                           | . 32 |

| AN-3535            | "An FM Tuner Using Single-Gate MOS Field-<br>Effect Transistors as RF Amplifier and Mixer" | . 38 |

| AN-4018            | "Design of Gate-Protected MOS Field-Effect Transistors"                                    | . 44 |

| AN-4125            | "MOS/FET Biasing Techniques"                                                               | . 57 |

| AN-4431            | "RF Applications of the Dual-Gate MOS/FET up to 500 MHz"                                   | . 64 |

| AN-4590            | "Using MOS/FET Integrated Circuits in Linear Circuit Applications"                         | . 71 |

# **Solid State Devices**

# Operating Considerations 1CE-402

# Operating Considerations for RCA Solid State Devices

Solid state devices are being designed into an increasing variety of electronic equipment because of their high standards of reliability and performance. However, it is essential that equipment designers be mindful of good engineering practices in the use of these devices to achieve the desired performance.

This Note summarizes important operating recommendations and precautions which should be followed in the interest of maintaining the high standards of performance of solid state devices.

The ratings included in RCA Solid State Devices data bulletins are based on the Absolute Maximum Rating System, which is defined by the following Industry Standard (JEDEC) statement:

Absolute-Maximum Ratings are limiting values of operating and environmental conditions applicable to any electron device of a specified type as defined by its published data, and should not be exceeded under the worst probable conditions.

The device manufacturer chooses these values to provide acceptable serviceability of the device, taking no responsibility for equipment variations, environmental variations, and the effects of changes in operating conditions due to variations in device characteristics.

The equipment manufacturer should design so that initially and throughout life no absolute-maximum value for the intended service is exceeded with any device under the worst probable operating conditions with respect to supply-voltage variation, equipment component variation, equipment control adjustment, load variation, signal variation, environmental conditions, and variations in device characteristics.

It is recommended that equipment manufacturers consult RCA whenever device applications involve unusual electrical, mechanical or environmental operating conditions.

# **GENERAL CONSIDERATIONS**

The design flexibility provided by these devices makes possible their use in a broad range of applications and under

many different operating conditions. When incorporating these devices in equipment, therefore, designers should anticipate the rare possibility of device failure and make certain that no safety hazard would result from such an occurrence.

The small size of most solid state products provides obvious advantages to the designers of electronic equipment. However, it should be recognized that these compact devices usually provide only relatively small insulation area between adjacent leads and the metal envelope. When these devices are used in moist or contaminated atmospheres, therefore, supplemental protection must be provided to prevent the development of electrical conductive paths across the relatively small insulating surfaces. For specific information on voltage creepage, the user should consult references such as the JEDEC Standard No. 7 "Suggested Standard on Thyristors," and JEDEC Standard RS282 "Standards for Silicon Rectifier Diodes and Stacks".

The metal shells of some solid state devices operate at the collector voltage and for some rectifiers and thyristors at the anode voltage. Therefore, consideration should be given to the possibility of shock hazard if the shells are to operate at voltages appreciably above or below ground potential. In general, in any application in which devices are operated at voltages which may be dangerous to personnel, suitable precautionary measures should be taken to prevent direct contact with these devices.

Devices should not be connected into or disconnected from circuits with the power on because high transient voltages may cause permanent damage to the devices.

#### TESTING PRECAUTIONS

In common with many electronic components, solid-state devices should be operated and tested in circuits which have reasonable values of current limiting resistance, or other forms of effective current overload protection. Failure to observe these precautions can cause excessive internal heating of the device resulting in destruction and/or possible shattering of the enclosure.

# TRANSISTORS AND THYRISTORS WITH FLEXIBLE LEADS

Flexible leads are usually soldered to the circuit elements. It is desirable in all soldering operatings to provide some slack or an expansion elbow in each lead to prevent excessive tension on the leads. It is important during the soldering operation to avoid excessive heat in order to prevent possible damage to the devices. Some of the heat can be absorbed if the flexible lead of the device is grasped between the case and the soldering point with a pair of pliers.

# TRANSISTORS AND THYRISTORS WITH MOUNTING FLANGES

The mounting flanges of JEDEC-type packages such as the TO-3 or TO-66 often serve as the collector or anode terminal. In such cases, it is essential that the mounting flange be securely fastened to the heat sink, which may be the equipment chassis. Under no circumstances, however, should the mounting flange of a transistor be soldered directly to the heat sink or chassis because the heat of the soldering operation could permanently damage the device. Soldering is the preferred method for mounting thyristors; see "Rectifiers and Thyristors," below. Devices which cannot be soldered can be installed in commercially available sockets. Electrical connections may also be made by soldering directly to the terminal pins. Such connections may be soldered to the pins close to the pin seals provided care is taken to conduct excessive heat away from the seals; otherwise the heat of the soldering operation could crack the pin seals and damage the device.

During operation, the mounting-flange temperature is higher than the ambient temperature by an amount which depends on the heat sink used. The heat sink must have sufficient thermal capacity to assure that the heat dissipated in the heat sink itself does not raise the device mounting-flange temperature above the rated value. The heat sink or chassis may be connected to either the positive or negative supply.

In many applications the chassis is connected to the voltage-supply terminal. If the recommended mounting hardware shown in the data bulletin for the specific solid-state device is not available, it is necessary to use either an anodized aluminum insulator having high thermal conductivity or a mica insulator between the mounting-flange and the chassis. If an insulating aluminum washer is required, it should be drilled or punched to provide the two mounting holes for the terminal pins. The burrs should then be removed from the washer and the washer anodized. To insure that the anodized insulating layer is not destroyed during mounting, it is necessary to remove the burrs from the holes in the chassis.

It is also important that an insulating bushing, such as glass-filled nylon, be used between each mounting bolt and the chassis to prevent a short circuit. However, the insulating bushing should not exhibit shrinkage or softening under the operating temperatures encountered. Otherwise the thermal resistance at the interface between device and heat sink may increase as a result of decreasing pressure.

# PLASTIC POWER TRANSISTORS AND THYRISTORS

RCA power transistors and thyristors (SCR's and triacs) in molded-silicone-plastic packages are available in a wide range of power-dissipation ratings and a variety of package configurations. The following paragraphs provide guidelines for handling and mounting of these plastic-package devices, recommend forming of leads to meet specific mounting requirements, and describe various mounting arrangements, thermal considerations, and cleaning methods. This information is intended to augment the data on electrical characteristics, safe operating area, and performance capabilities in the technical bulletin for each type of plastic-package transistor or thyristor.

### Lead-Forming Techniques

The leads of the RCA VERSAWATT in-line plastic packages can be formed to a custom shape, provided they are not indiscriminately twisted or bent. Although these leads can be formed, they are not flexible in the general sense, nor are they sufficiently rigid for unrestrained wire wrapping

Before an attempt is made to form the leads of an in-line package to meet the requirements of a specific application, the desired lead configuration should be determined, and a lead-bending fixture should be designed and constructed. The use of a properly designed fixture for this operation eliminates the need for repeated lead bending. When the use of a special bending fixture is not practical, a pair of long-nosed pliers may be used. The pliers should hold the lead firmly between the bending point and the case, but should not touch the case.

When the leads of an in-line plastic package are to be formed, whether by use of long-nosed pliers or a special bending fixture, the following precautions must be observed to avoid internal damage to the device:

- Restrain the lead between the bending point and the plastic case to prevent relative movement between the lead and the case.

- 2. When the bend is made in the plane of the lead (spreading), bend only the narrow part of the lead.

- When the bend is made in the plane perpendicular to that

of the leads, make the bend at least 1/8 inch from the

plastic case.

- 4. Do not use a lead-bend radius of less than 1/16 inch.

- 5. Avoid repeated bending of leads.

The leads of the TO-220AB VERSAWATT in-line package are not designed to withstand excessive axial pull. Force in this direction greater than 4 pounds may result in permanent damage to the device. If the mounting arrangement tends to impose axial stress on the leads, some method of strain relief should be devised.

Wire wrapping of the leads is permissible, provided that the lead is restrained between the plastic case and the point of the wrapping. Soldering to the leads is also allowed. The maximum soldering temperature, however, must not exceed 275°C and must be applied for not more than 5 seconds at a distance not less than 1/8 inch from the plastic case. When

wires are used for connections, care should be exercised to assure that movement of the wire does not cause movement of the lead at the lead-to-plastic junctions.

The leads of RCA molded-plastic high-power packages are not designed to be reshaped. However, simple bending of the leads is permitted to change them from a standard vertical to a standard horizontal configuration, or conversely. Bending of the leads in this manner is restricted to three 90-degree bends; repeated bendings should be avoided.

#### Mounting

Recommended mounting arrangements and suggested hardward for the VERSAWATT package are given in the data bulletins for specific devices and in RCA Application Note AN-4142. When the package is fastened to a heat sink, a rectangular washer (RCA Part No. NR231A) is recommended to minimize distortion of the mounting flange. Excessive distortion of the flange could cause damage to the package. The washer is particularly important when the size of the mounting hole exceeds 0.140 inch (6-32 clearance). Larger holes are needed to accommodate insulating bushings; however, the holes should not be larger than necessary to provide hardware clearance and, in any case, should not exceed a diameter of 0.250 inch.

Flange distortion is also possible if excessive torque is used during mounting. A maximum torque of 8 inch-pounds is specified. Care should be exercised to assure that the tool used to drive the mounting screw never comes in contact with the plastic body during the driving operation. Such contact can result in damage to the plastic body and internal device connections. An excellent method of avoiding this problem is to use a spacer or combination spacer-isolating bushing which raises the screw head or nut above the top surface of the plastic body. The material used for such a spacer or spacer-isolating bushing should, of course, be carefully selected to avoid "cold flow" and consequent reduction in mounting force. Suggested materials for these bushings are diallphtalate, fiberglass-filled nylon, or fiberglass-filled polycarbonate. Unfilled nylon should be avoided.

Modification of the flange can also result in flange distortion and should not be attempted. The package should not be soldered to the heat sink by use of lead-tin solder because the heat required with this type of solder will cause the junction temperature of the device to become excessively high.

The TO-220AA plastic package can be mounted in commercially available TO-66 sockets, such as UID Electronics Corp. Socket No. PTS-4 or equivalent. For testing purposes, the TO-220AB in-line package can be mounted in a Jetron Socket No. DC74-104 or equivalent. Regardless of the mounting method, the following precautions should be taken:

- 1. Use appropriate hardware.

- Always fasten the package to the heat sink before the leads are soldered to fixed terminals.

- 3. Never allow the mounting tool to come in contact with the plastic case.

- 4. Never exceed a torque of 8 inch-pounds.

- 5. Avoid oversize mounting holes.

- 6. Provide strain relief if there is any probability that axial stress will be applied to the leads.

- Use insulating bushings to prevent hot-creep problems. Such bushings should be made of diallphthalate, fiberglass-filled nylon, or fiberglass-filled polycarbonate.

The maximum allowable power dissipation in a solid state device is limited by the junction temperature. An important factor in assuring that the junction temperature remains below the specified maximum value is the ability of the associated thermal circuit to conduct heat away from the device.

When a solid state device is operated in free air, without a heat sink, the steady-state thermal circuit is defined by the junction-to-free-air thermal resistance given in the published data for the device. Thermal considerations require that a free flow of air around the device is always present and that the power dissipation be maintained below the level which would cause the junction temperature to rise above the maximum rating. However, when the device is mounted on a heat sink, care must be taken to assure that all portions of the thermal circuit are considered.

To assure efficient heat transfer from case to heat sink when mounting RCA molded-plastic solid state power devices, the following special precautions should be observed:

- Mounting torque should be between 4 and 8 inchpounds.

- 2. The mounting holes should be kept as small as possible.

- Holes should be drilled or punched clean with no burrs or ridges, and chamfered to a maximum radius of 0.010 inch.

- 4. The mounting surface should be flat within 0.002 inch/inch.

- Thermal grease (Dow Corning 340 or equivalent) should always be used on both sides of the insulating washer if one is employed.

- Thin insulating washers should be used. (Thickness of factory-supplied mica washers range from 2 to 4 mils).

- A lock washer or torque washer, made of material having sufficient creep strength, should be used to prevent degradation of heat sink efficiency during life.

A wide variety of solvents is available for degreasing and flux removal. The usual practice is to submerge components in a solvent bath for a specified time. However, from a reliability stand point it is extremely important that the solvent, together with other chemicals in the solder-cleaning system (such as flux and solder covers), do not adversely affect the life of the component. This consideration applies to all non-hermetic and molded-plastic components.

It is, of course, impractical to evaluate the effect on long-term device life of all cleaning solvents, which are marketed with numerous additives under a variety of brand names. These solvents can, however, be classified with respect to their component parts as either acceptable or unacceptable. Chlorinated solvents tend to dissolve the outer package and, therefore, make operation in a humid atmosphere unreliable. Gasoline and other hydrocarbons cause the inner encapsulant to swell and damage the transistor. Alcohol is an acceptable solvent. Examples of specific, acceptable alchols are isopropanol, methanol, and special denatured alcohols, such as SDA1, SDA30, SDA34, and SDA44.

Care must also be used in the selection of fluxes for lead soldering. Rosin or activated rosin fluxes are recommended, while organic or acid fluxes are not. Examples of acceptable fluxes are:

- 1. Alpha Reliaros No. 320-33

- 2. Alpha Reliaros No. 346

- 3. Alpha Reliaros No. 711

- 4. Alpha Reliafoam No. 807

- 5. Alpha Reliafoam No. 809

- 6. Alpha Reliafoam No. 811-13

- 7. Alpha Reliafoam No. 815-35

- 8. Kester No. 44

If the completed assembly is to be encapsulated, the effect on the molded-plastic transistor must be studied from both a chemical and a physical standpoint.

### RECTIFIERS AND THYRISTORS

A surge-limiting impedance should always be used in series with silicon rectifiers and thyristors. The impedance value must be sufficient to limit the surge current to the value specified under the maximum ratings. This impedance may be provided by the power transformer winding, or by an external resistor or choke.

A very efficient method for mounting thyristors utilizing the "modified TO-5" package is to provide intimate contact between the heat sink and at least one half of the base of the device opposite the leads. This package can be mounted to the heat sink mechanically with glue or an expoxy adhesive, or by soldering, the most efficient method.

The use of a "self-jigging" arrangement and a solder preform is recommended. If each unit is soldered individually, the heat source should be held on the heat sink and the solder on the unit. Heat should be applied only long enough to permit solder to flow freely. For more detailed thyristor mounting considerations, refer to Application Note AN3822, "Thermal Considerations in Mounting of RCA Thyristors".

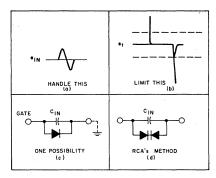

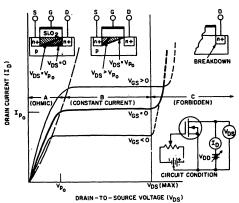

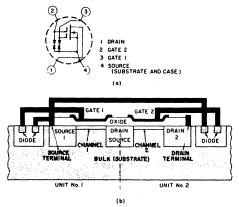

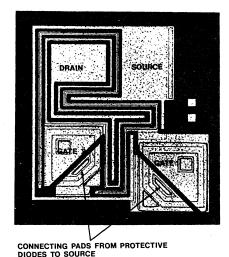

## MOS FIELD-EFFECT TRANSISTORS

Insulated-Gate Metal Oxide-Semiconductor Field-Effect Transistors (MOS FETs), like bipolar high-frequency transistors, are susceptible to gate insulation damage by the electrostatic discharge of energy through the devices. Electrostatic discharges can occur in an MOS FET if a type with an unprotected gate is picked up and the static charge, built in the handler's body capacitance, is discharged through the device. With proper handling and applications procedures, however, MOS transistors are currently being extensively used in production by numerous equipment manufacturers in military, industrial, and consumer applica-

tions, with virtually no problems of damage due to electrostatic discharge.

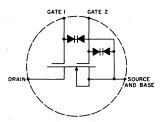

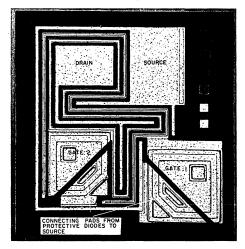

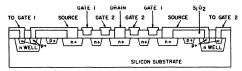

In some MOS FETs, diodes are electrically connected between each insulated gate and the transistor's source. These diodes offer protection against static discharge and in-circuit transients without the need for external shorting mechanisms. MOS FETs which do not include gate-protection diodes can be handled safely if the following basic precautions are taken:

- Prior to assembly into a circuit, all leads should be kept shorted together either by the use of metal shorting springs attached to the device by the vendor, or by the insertion into conductive material such as "ECCOSORB\* LD26" or equivalent.

- (NOTE: Polystyrene insulating "SNOW" is not sufficiently conductive and should not be used.)

- When devices are removed by hand from their carriers, the hand being used should be grounded by any suitable means, for example, with a metallic wristband.

- 3. Tips of soldering irons should be grounded.

- Devices should never be inserted into or removed from circuits with power on.

#### RF POWER TRANSISTORS

# Mounting and Handling

Stripline rf devices should be mounted so that the leads are not bent or pulled away from the stud (heat sink) side of the device. When leads are formed, they should be supported to avoid transmitting the bending or cutting stress to the ceramic portion of the device. Excessive stresses may destroy the hermeticity of the package without displaying visible damage.

Devices employing silver leads are susceptible to tarnishing; these parts should not be removed from the original tarnish-preventive containers and wrappings until ready for use. Lead solderability is retarded by the presence of silver tarnish; the tarnish can be removed with a silver cleaning solution, such as thiourea.

The ceramic bodies of many rf devices contain beryllium oxide as a major ingredient. These portions of the transistors should not be crushed, ground, or abraded in any way because the dust created could be hazardous if inhaled.

#### Operating

Forward-Biased Operation. For Class A or AB operation, the allowable quiescent bias point is determined by reference to the infrared safe-area curve in the appropriate data bulletin. This curve depicts the safe current/voltage combinations for extended continuous operation.

Load VSWR. Excessive collector load or tuning mismatch can cause device destruction by over-dissipation or secondary breakdown. Mismatch capability is generally included on the data bulletins for the more recent rf transistors.

See RCA RF Power Transitor Manual, Technical Series RMF-430, pp 39-41, for additional information concerning the handling and mounting of rf power transistors.

<sup>\*</sup>Trade Mark: Emerson and Cumming, Inc.

### INTEGRATED CIRCUITS

### Handing

All COS/MOS gate inputs have a resistor/diode gate protection network. All transmission gate inputs and all outputs have diode protection provided by inherent p-n junction diodes. These diode networks at input and output interfaces protect COS/MOS devices from gate-oxide failure in handling environments where static discharge is not excessive. In low-temperature, low-humidity environments, improper handling may result in device damage. See ICAN-6000, "Handling and Operating Considerations for MOS Integrated Circuits", for proper handling procedures.

#### Mounting

Integrated circuits are normally supplied with lead-tin plated leads to facilitate soldering into circuit boards. In those relatively few applications requiring welding of the device leads, rather than soldering, the devices may be obtained with gold or nickel plated Kovar leads.\* It should be recognized that this type of plating will not provide complete protection against lead corrosion in the presence of high humidity and mechanical stress. The aluminum-foil-lined cardboard "sandwich pack" employed for static protection of the flat-pack also provides some additional protection against lead corrosion, and it is recommended that the devices be stored in this package until used.

When integrated circuits are welded onto printed circuit boards or equipment, the presence of moisture between the closely spaced terminals can result in conductive paths that may impair device performance in high-impedance applications. It is therefore recommended that conformal coatings or potting be provided as an added measure of protection against moisture penetration.

In any method of mounting integrated circuits which involves bending or forming of the device leads, it is extremely important that the lead be supported and clamped between the bend and the package seal, and that bending be done with care to avoid damage to lead plating. In no case should the radius of the bend be less than the diameter of the lead, or in the case of rectangular leads, such as those used in RCA 14-lead and 16-lead flat-packages, less than the lead thickness. It is also extremely important that the ends of the bent leads be straight to assure proper insertion through the holes in the printed-circuit board.

### Operating

# **Unused Inputs**

All unused input leads must be connected to either VSS or VDD, whichever is appropriate for the logic circuit involved. A floating input on a high-current type, such as the CD4049 or CD4050, not only can result in faulty logic operation, but can cause the maximum power dissipation of 200 milliwatts to be exceeded and may result in damage to the device. Inputs to these types, which are mounted on printed-circuit boards that may temporarily become unterminated, should have a pull-up resistor to VSS or VDD. A useful range of values for such resistors is from 10 kilohms to 1 megohm.

#### Input Signals

Signals shall not be applied to the inputs while the device power supply is off unless the input current is limited to a steady state value of less than 10 milliamperes. Input currents of less than 10 milliamperes prevent device damage; however, proper operation may be impaired as a result of current flow through structural diode junctions.

### **Output Short Circuits**

Shorting of outputs to VSS or VDD can damage many of the higher-output-current COS/MOS types, such as the CD4007, CD4041, CD4049, and CD4050. In general, these types can all be safely shorted for supplies up to 5 volts, but will be damaged (depending on type) at higher power-supply voltages. For cases in which a short-circuit load, such as the base of a p-n-p or an n-p-n bipolar transistor, is directly driven, the device output characteristics given in the published data should be consulted to determine the requirements for a safe operation below 200 milliwatts.

For detailed COS/MOS IC operating and handling considerations, refer to Application Note ICAN-6000 "Handling and Operating Considerations for MOS Integrated Circuits".

# SOLID STATE CHIPS

Solid state chips, unlike packaged devices, are nonhermetic devices, normally fragile and small in physical size, and therefore, require special handling considerations as follows:

- Chips must be stored under proper conditions to insure that they are not subjected to a moist and/or contaminated atmosphere that could alter their electrical, physical, or mechanical characteristics. After the shipping container is opened, the chip must be stored under the following conditions:

- A. Storage temperature, 40°C max.

- B. Relative humidity, 50% max.

- C. Clean, dust-free environment.

- The user must exercise proper care when handling chips to prevent even the slightest physical damage to the chip.

- During mounting and lead bonding of chips the user must use proper assembly techniques to obtain proper electrical, thermal, and mechanical performance.

- 4. After the chip has been mounted and bonded, any necessary procedure must be followed by the user to insure that these non-hermetic chips are not subjected to moist or contaminated atmosphere which might cause the development of electrical conductive paths across the relatively small insulating surfaces. In addition, proper consideration must be given to the protection of these devices from other harmful environments which could conceivably adversely affect their proper performance.

<sup>\*</sup>Mil-M-38510A, paragraph 3.5.6.1 (a), lead material.

# **MOS Field-Effect Transistors**

Application Note AN-3193

# Application Considerations for the RCA 3N128 VHF MOS Field-Effect Transistor

bу

F. M. Carlson

Early MOS field-effect transistors were intended primarily for low-frequency applications in which their extremely high input impedance is advantageous, and were not designed to be useful in the vhf range (30 to 300 MHz). Recently, however, RCA has developed high-frequency MOS transistors that exhibit high gain and low noise at vhf, together with very low feedback capacitance and cross-modulation distortion that approaches the low levels of electron tubes. The low level of cross-modulation distortion is a particularly important characteristic in view of the increasing congestion of the communications frequency bands.

This note describes applications and vhf circuit considerations for a new high-frequency n-channel MOS field-effect transistor, the RCA 3N128. Biasing requirements and basic circuit configurations are discussed, and selection of the optimum operating point and methods of automatic gain control are explained. The cross-modulation and intermodulation distortion characteristics of the 3N128 MOS transistor are compared to those of bipolar transistors, and procedures are given for the design of a practical vhf amplifier that uses the 3N128.

# Biasing Requirements and Circuit Configurations

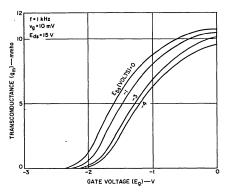

The biasing requirements and operating characteristics of an n-channel MOS transistor such as the

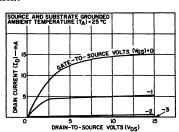

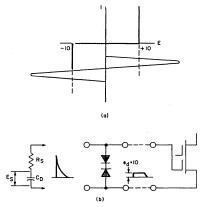

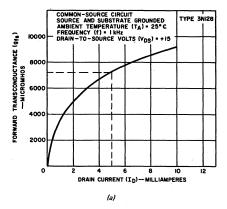

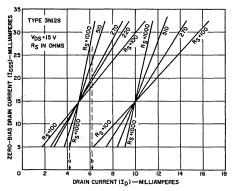

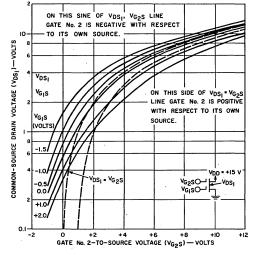

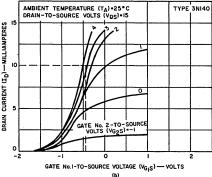

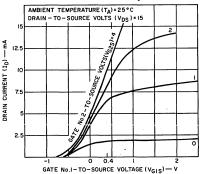

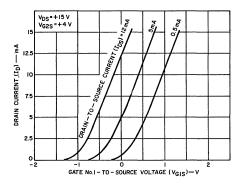

3N128 are similar to those of an electron tube. For example, the 3N128 uses positive drain voltages and usually negative gate voltages which are analogous to the plate and grid voltages, respectively, of electron tubes. In addition, the current-voltage characteristics of the 3N128, shown in Fig.1, are similar to those of a pentode tube. An electron-tube analogy, therefore, can be useful in the analysis of the n-channel 3N128 MOS transistor.

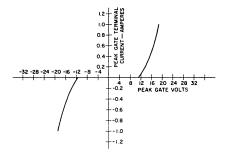

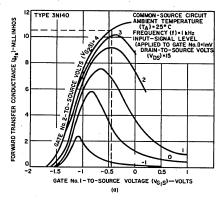

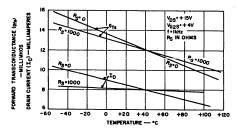

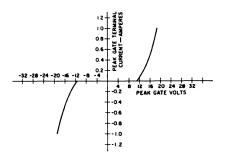

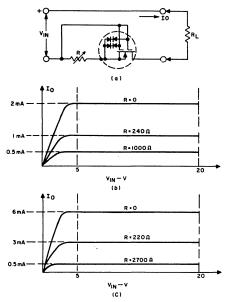

Fig.1 - Transfer characteristics for the RCA 3N128

Although their characteristics are similar, MOS transistors have several important advantages over electron tubes. They can be operated at the low voltages typical of bipolar transistors. The dc gate current of MOS transistors is substantially less than the

<sup>&</sup>lt;sup>†</sup> The electron-tube analogy does not apply to p-channel MOS transistors or to enhancement types.

grid current of most electron tubes. In addition, the MOS transistor requires no heat-generating filament.

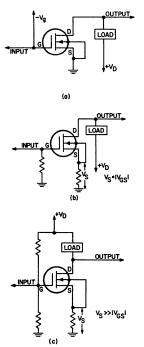

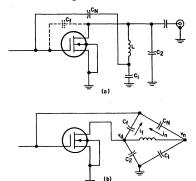

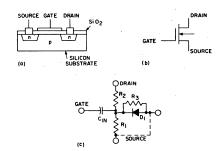

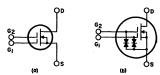

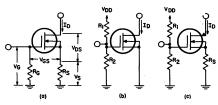

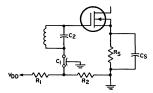

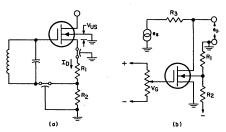

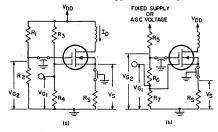

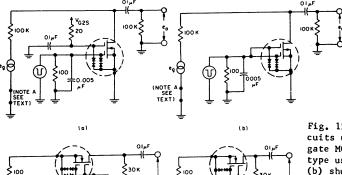

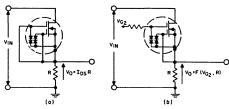

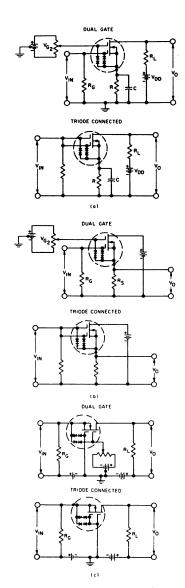

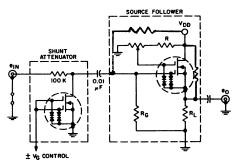

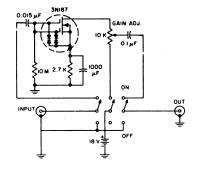

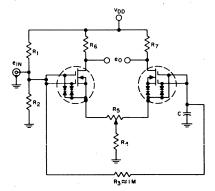

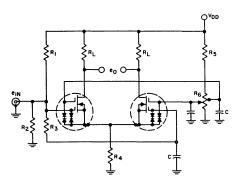

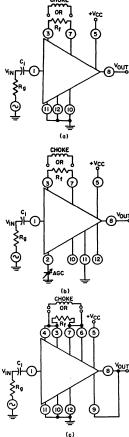

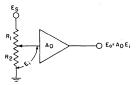

MOS transistors are most often used in the commonsource type of circuit configuration. Fig. 2 shows three basic methods of dc-biasing an MOS transistor in a common-source circuit. MOS transistors may also be used in common-gate or common-drain (source-follower) configurations. <sup>2</sup> These circuits are not widely used in vhf applications, however, because their gain is low at high frequencies.

Fig.2 - Bias methods for common-source MOS transistor stages: (a) fixed bias; (b) source-resistor bias; (c) constant-current bias.

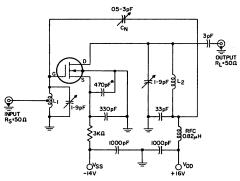

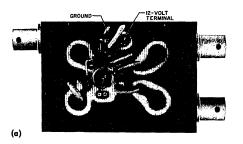

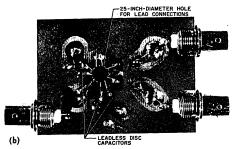

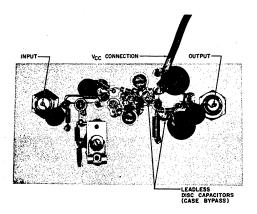

Fig.3 shows a 200-MHz common-source amplifier used to measure the rf power gain of the MOS transistor. This amplifier uses a modified form of the constant-current biasing arrangement shown in Fig.2(c). With this modified biasing arrangement, both the insulated gate and the case of the MOS transistor are operated at dc ground potential. The insulated gate should always have a dc path to ground even if the path is through a multimegohm resistor. If the gate is allowed to float, the resultant dc bias conditions may be unpredictable and possibly harmful.

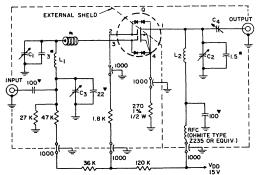

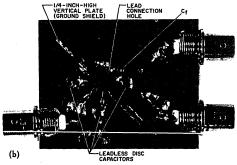

- L<sub>1</sub> = 4-1/2 turns of No.20 wire, 3/16 inch in dia., 1/2 inch long, tapped at 1 turn

- L<sub>2</sub> = 3-1/2 turns of No.20 wire, 3/8 inch in dia.,

- \* Leadless disc capacitor

Fig.3 - 200-MHz common-source amplifier.

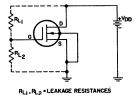

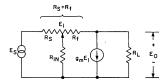

Fig.4 illustrates the effect of the leakage resistances  $R_{L\,1}$  and  $R_{L\,2}$  when the insulated gate is floating. When these resistances  $(\approx 10^{14}~\rm ohms)$  are approximately equal, they form a voltage divider which biases the insulated gate at +V\_DD/2. This value of bias voltage may exceed the maximum rating for positive gate voltage and, in addition, may cause an excessive flow of drain current.

Fig.4 - Bias conditions for an MOS transistor when the insulated gate is floating.

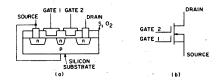

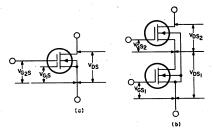

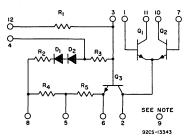

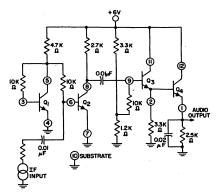

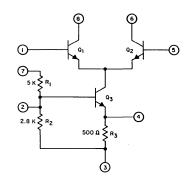

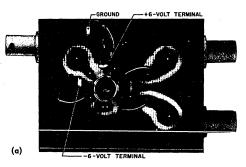

The cascode configuration represents a useful variation of common-source circuit. In this configuration, a common-source-connected MOS transistor is used in the lower section of the cascode, and a common-gate-connected MOS transistor is used in the upper section. Fig.5 shows the use of MOS transistors in a 200-MHz cascode amplifier. This circuit normally requires a negative voltage on the gate of  $Q_1$ , and approximately equal drain-to-source voltages for each transistor. Although the gate of  $Q_2$  may require a positive voltage of 5 to 10 volts, the net gate-to-source voltage for this transistor should be approximately 0 to -1 volt.

Fig.5 - 200-MHz cascode amplifier.

# Selection of Operating Point

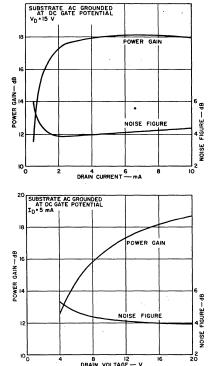

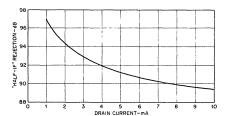

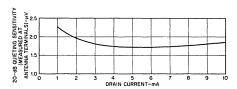

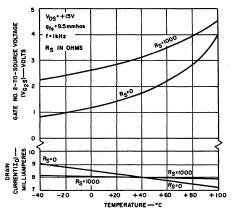

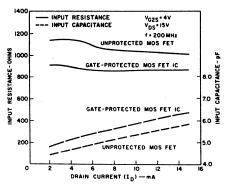

The operating point selected determines the power gain, noise figure, power dissipation, and, where applicable, battery life. In many applications, a compromise between gain and available supply voltages or battery lifetime is necessary. Knowledge of the variation in gain and noise figure as functions of voltage and current is essential, therefore, before an operating point can be selected.

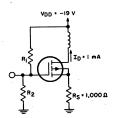

The 3N128 provides maximum rf power gain at a drain-to-source voltage  $V_{\rm DS}$  of approximately 20 volts and a drain current  $I_{\rm D}$  of about 5 milliamperes. The transistor also exhibits a minimum noise figure at a  $V_{\rm DS}$  of 20 volts for a drain current of about 2 milliamperes. The difference in the noise figures obtained at 2 milliamperes and at 5 milliamperes, however, is very small (usually between 0 and 0.2 dB) and generally is not a significant factor in the selection of the operating point. Although a  $V_{\rm DS}$  of 20 volts represents the optimum value for the 3N128 in terms of both rf power gain and noise figure, this value is also the maximum  $V_{\rm DS}$  rating for the transistor. Greater long-term reliability is achieved, therefore, by operation of the 3N128 at a  $V_{\rm DS}$  of 12 to 15 volts rather than at 20 volts.

For a  $V_{\rm DS}$  of 15 volts and an  $I_{\rm D}$  of 5 milliamperes, the 3N128 typically provides a power gain of 18 dB and a noise figure of 4 dB at 200 MHz. Operation of the 3N128 at considerably lower drain currents, such as those normally employed in battery-powered equipment, does not seriously affect system performance. For example, when the transistor is operated at a  $V_{\rm DS}$  of 15 volts and an  $I_{\rm D}$  of only 1 milliampere, the power gain and noise figure at 200 MHz are typically 15.5 dB and 4.5 dB, respectively. Because the MOS transistor is a voltage-controlled device, its performance for a given power dissipation can often be improved by operation at high voltage and low current levels. At a power

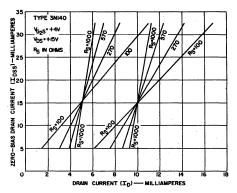

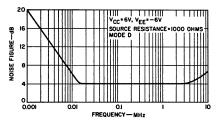

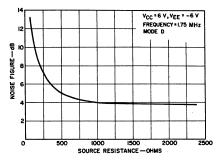

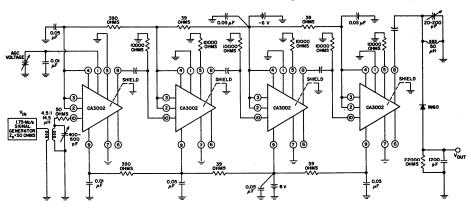

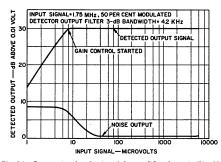

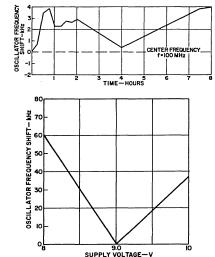

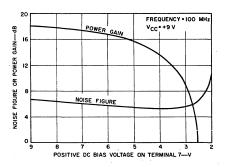

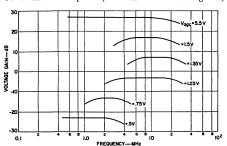

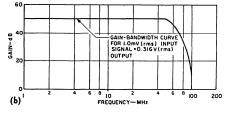

dissipation of 30 milliwatts, for example, the 3N128 typically provides a power gain of 17.3 dB and a noise figure of 3.9 dB when operated at 15 volts and 2 milliamperes. At the same dissipation level, however, the power gain is reduced to 14.6 dB and the noise figure is increased to 4.7 dB when the 3N128 is operated at 6 volts and 5 milliamperes. Fig.6 shows the variations in power gain and noise figure of the 3N128 as functions of the drain current and voltage.

Fig.6 - Power gain and noise figure of the RCA 3N128 at 200 MHz as functions of drain current and voltage.

A gate voltage  $V_G$  of between -0.5 and -2 volts is normally required to bias a 3N128 for operation at a drain voltage  $V_D$  of 15 volts and a drain current  $I_D$  of 5 milliamperes. If a fixed-bias circuit, as shown in Fig.2(a), is used, the value of the gate voltage must be adjustable to compensate for variations among individual transistors. For the source-resistance bias circuit shown in Fig.2(b) the value of the biasing resistor should be 200 ohms (5 mA x 200 ohms = 1 volt). The source-resistance circuit will limit the variations in current among the different transistors to approximately

With the constant-current bias circuit 50 per cent. shown in Fig.2(c), variations in current from one transistor to another can easily be limited to less than 10 per cent. Regardless of the bias circuit or the bias point selected, there is no danger of thermal runaway with the 3N128 because this transistor has a negative temperature coefficient at the zero-gate-bias point. In the selection of the bias circuit for an MOS transistor stage in which automatic gain control is employed, consideration should be given to the following principle: The more restrictive the tolerance imposed on quiescent operating-point current, the more difficult automatic gain control of the stage becomes because the selfcompensating action of the constant-current bias circuit also resists current changes that result from the ago action.

# AGC Methods

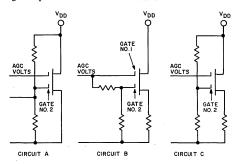

When it is necessary to employ agc in an MOS transistor stage, either of two methods may be used to reduce transistor gain. In one method, referred to as reverse agc, the reduction in gain is accomplished by an increase in negative gate bias. In the other method, the gain is decreased by reduction of the drain-to-source voltage.

In the reverse agc method, the application of higher negative voltage to the gate reduces the drain current and the transconductance of the transistor. The low feedthrough capacitance of the 3N128 (typically about 0.13 picofarad) usually permits more than 30 dB of gain reduction at frequencies up to 200 MHz. Substantially greater gain reduction can be achieved at lower frequencies or in neutralized amplifier circuits.

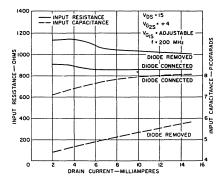

Gain reduction achieved by the decrease of drain-to-source voltage is usually controlled by a variable impedance in series, or in shunt, with the MOS transistor. The variable impedance may be another MOS transistor or a bipolar transistor. A major disadvantage of this method is that the MOS feedback capacitance rises by a factor of 4 or 6 times as  $V_{\rm D}$  approaches zero. This increase in capacitance reduces the ago range obtainable and decreases the effectiveness of a fixed neutralization network. In addition, the output impedance of the 3N128 decreases with a reduction in the drain voltage.

In the cascode circuit, age is accomplished most effectively by application of a negative voltage to the gate of the upper (common-gate) section. A wide age range can be obtained in this circuit. Gain reductions greater than 45 dB at 200 MHz or 65 dB at 60 MHz are realizable in an unneutralized cascode circuit.

### RF Considerations

One of the prime advantages of the 3N128 MOS transistor over bipolar transistors is its superior cross-

modulation, intermodulation, and modulation distortion performance. The 3N128 has considerably lower feedback capacitance than junction-gate field-effect transistors. In addition, the 3N128 maintains a high input resistance at frequencies well into the vhf range (the real part of the input admittance,  $Re(y_{11}) = 0.15 \text{ mmho}$  at 100 MHz).

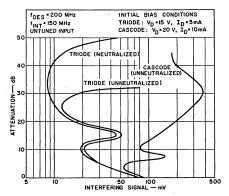

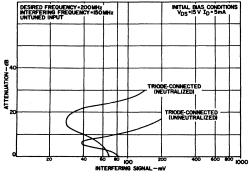

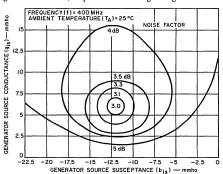

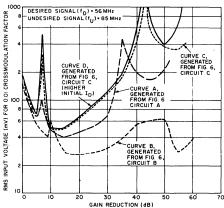

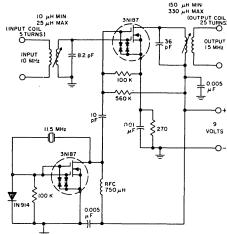

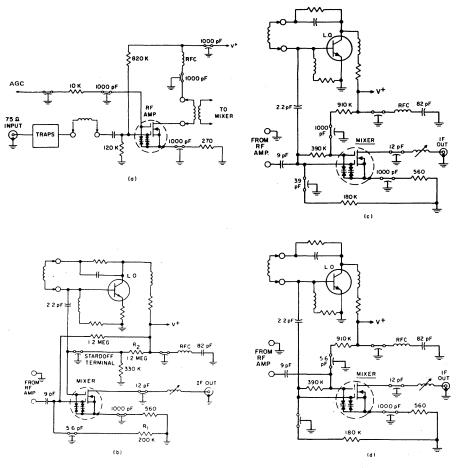

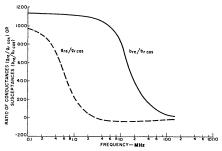

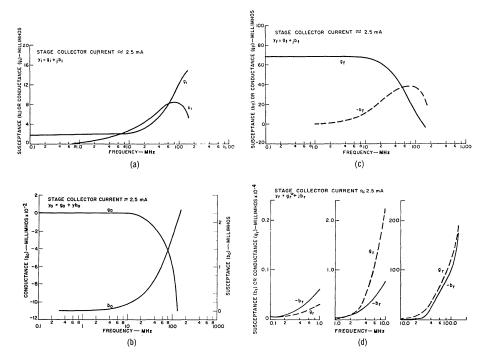

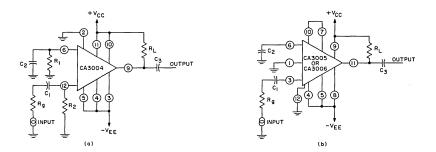

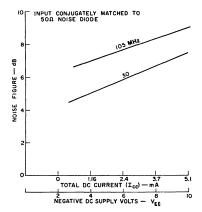

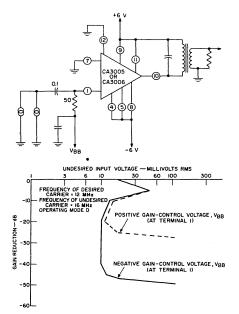

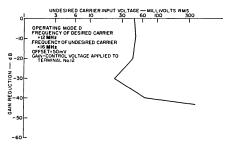

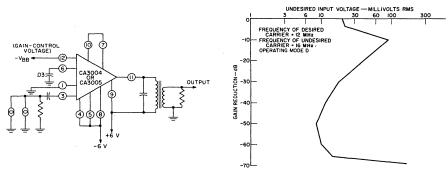

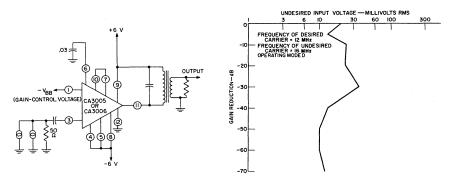

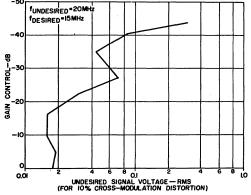

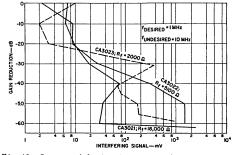

At maximum gain, the cross-modulation distortion of the 3N128 is approximately one-tenth that of most bipolar transistors, or roughly comparable to the crossmodulation performance of vacuum tubes (at 200 MHz, an interfering signal of approximately 80 millivolts is required to produce cross-modulation distortion of 1 per cent). However, cross-modulation susceptibility changes as the gain of the stage is changed. For a single 3N128, the cross-modulation distortion increases when reverse age is applied; the distortion is also increased, but to a lesser extent, if agc action is achieved by reduction of the drain-to-source voltage. A deterioration in cross-modulation performance at high attenuation results from the fact that the MOS triode is a sharpcutoff device; as a result, large non-linearities occur near "pinch-off." Beyond "pinch-off," the transadmittance depends primarily upon the capacitive feedthrough, which does not have large third-order nonlinearities. Cross-modulation performance at the extreme limits of attenuation, therefore, is very good. 1 In cascode stages, the effect of reverse agc on crossmodulation distortion is reduced when the age is applied to the gate of the common-gate stage; application of reverse bias to the gate of the common-source stage results in cross-modulation performance similar to that of a single triode-connected stage. Figs.7 and 8 show the variation in cross-modulation susceptibility as a function of agc. The test circuits used to measure cross-modulation distortion of MOS transistors are shown in Fig.9.

Fig.7 - Cross-modulation distortion as a function of the attenuation produced by reverse agc.

Fig.8 - Cross-modulation distortion as a function of the attenuation produced when agc is accomplished by a reduction of drain-to-source voltage.

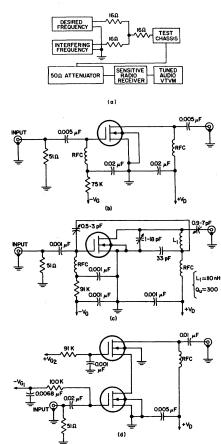

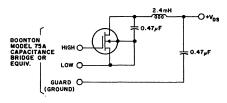

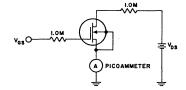

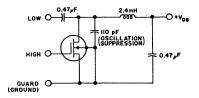

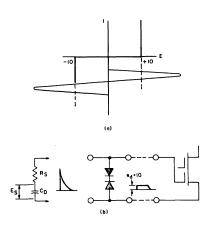

The test circuit shown in Fig. 10 is used to measure the intermodulation distortion of MOS transistors. In such measurements, the receiver is tuned to 150 MHz. The MOS is then inserted, and bias voltages are applied. When no signals are applied (i.e., the amplitudes of the signals f1 and f2 are both 0 volts), the rf indicator of the receiver indicates an equivalent input noise level of approximately 2.4 microvolts. The signals f1 and f2 are gradually increased in amplitude until the reading on the rf indicator is 1 microvolt above the noise level (3.4 microvolts total). This reading indicates that 2.4 microvolts of 150-MHz signal is being produced by the interaction of f1 and f2 (i.e., 2 f1-f2 = 150 MHz). Table I lists the dc bias levels used for the 3N128 MOS transistor and the amplitude of the f1 and f<sub>2</sub> signals required to produce an output, at 150 MHz, of 2.4 microvolts, which corresponds to 1 microvolt above the input noise level. The amplitudes of f1 and f2 were measured by an rf vacuum-tube voltmeter; the f<sub>1</sub> generator was turned down for measurement of f<sub>2</sub>, and vice versa.

Table I

INTERMODULATION DISTORTION DATA

FOR THE 3N128 MOS TRANSISTOR

Interfering Voltages Required to Produce 2.4 microvolts at 150 MHz

|             |          | 2.4 microvoria di 150 mili |                    |  |  |

|-------------|----------|----------------------------|--------------------|--|--|

| VD<br>volts | ID<br>mA | f1 (175 MHz)<br>mV         | f2 (200 MHz)<br>mV |  |  |

| 16.5        | 10       | 18                         | 18                 |  |  |

| 16.5        | 10       | 7                          | 150                |  |  |

| 16.5        | 5        | 15                         | 15                 |  |  |

| 16.5        | 5        | 3.5                        | 150                |  |  |

| 16.5        | 5        | . 30                       | 3.5                |  |  |

| 16.5        | 2.5      | 19                         | 21                 |  |  |

When the same test methods were used to measure the intermodulation distortion of bipolar transistors, distortion levels were found to be two to five times greater than those of the 3N128 MOS transistor.

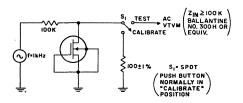

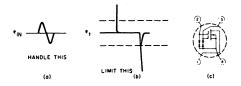

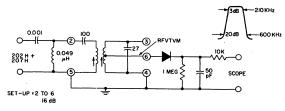

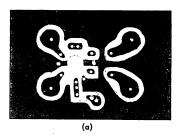

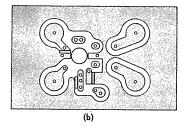

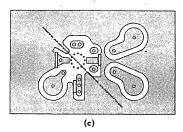

Fig.9 - Test circuits used to measure cross-modulation distortion in MOS transistors: (a) block diagram;

(b) unneutralized-stage test circuit;

(c) neutralized-stage test circuit;(d) cascode-stage test circuit.

# Designing VHF MOS Amplifier Circuits

A complete set of graphs of typical y parameters, both as a function of frequency at constant bias and as as a function of bias at constant frequency, are given in the published data for the 3N128 MOS transistor. The application of these y parameters in the design of the 200-MHz amplifier shown in Fig.3 is discussed in following paragraphs.

For operation at a frequency of 200 MHz, an ID of

Fig. 10 - Test circuit used to measure intermodulation distortion in MOS transistors.

5 milliamperes, and a  $V_D$  of 15 volts, the y parameters of the 3N128 are typically as follows:

y<sub>11</sub> (input admittance with output short-circuited) = 0.45 + i7.2 mmhos

y<sub>22</sub> (output admittance with input short-circuited) = 0.28 + j1.75 mmhos

y<sub>21</sub> (forward transfer admittance with output short-circuited) = 7.0 - j 1.9 mmhos

y<sub>12</sub> (reverse transfer admittance with input short-circuited) = 0 - j0.16 mmhos

If  $y_{12}$  is assumed to be zero, the maximum available power gain (MAG) under conjugately matched conditions,\* may be computed. MAG serves as a useful figure of merit for comparison of the vhf power gain of various MOS transistors. The MAG for the 3N128 is determined as follows:

MAG =

$$\frac{|y_{21}|^2}{4\text{Re}(y_{11})\text{Re}(y_{22})} = \frac{|7.0 - \text{j}1.9|^2}{4(0.45)(0.28)} = 104 = 20.2 \,\text{dB}$$

(1)

where Re means "the real part of."

All MOS transistors have a small, but measurable, feedback component (y<sub>12</sub>); it is possible, therefore, that some of them will oscillate under certain circuit conditions. This possibility may be checked by use of methods given by Linvill<sup>2,4</sup> and by Stern.<sup>3,4</sup> If the transistor is unconditionally stable for any combination of passive source and load admittances, then Linvill's critical stability factor C, as determined from the following equation, is less than | 1 |:

$$C = \frac{|y_{21}y_{12}|}{2\text{Re}(y_{11})\text{Re}(y_{22})-\text{Re}(y_{21}y_{12})}$$

(2)

The critical stability factor for the 3N128 is calculated as follows:

$$C = \frac{\left| (7.0 - j1.9)(0 - j0.16) \right|}{2(0.45)(0.28) - \text{Re}(7.0 - j1.9)(-j0.16)} = 2.08$$

Stern has derived a similar expression for stability  $C_S$  that includes the effect of the generator and load conductances,  $y_g$  and  $y_L$ , respectively, as follows:

$$C_{s} = \frac{\left|y_{21}y_{12}\right|}{2 \operatorname{Re}(y_{11} + y_{g}) \operatorname{Re}(y_{22} + y_{L}) - \operatorname{Re}(y_{21}y_{12})} < \left|1\right| \quad \text{(3)}$$

If a conjugate match is assumed at both the input and the output, then  $\operatorname{Re}(y_g) = \operatorname{Re}(y_{11})$ , and  $\operatorname{Re}(y_L) = \operatorname{Re}(y_{22})$ . For this condition, the stability factor is calculated as follows:

$$C_{S} = \frac{\left| (7.0\text{-}j1.9)(\text{-}j0.16) \right|}{2(0.45 + 0.45)(0.28 + 0.28) \cdot \text{Re}(7.0\text{-}j1.9)(\text{-}j0.16)} = \frac{1.16}{1.31} = 0.885$$

These calculations show that the transistor itself is not unconditionally stable, but that it is stable when placed in a conjugately matched circuit. Therefore, neutralization is not required, although it may be used if a more symmetrical pass-band characteristic is desired. All unneutralized amplifiers have a certain amount of skew in the selectivity characteristic; if this skewness becomes objectionable for the required application, then neutralization (or mis-matching) is necessary.

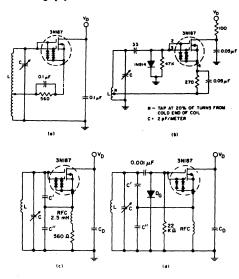

When neutralization is desired, there are two common methods of obtaining the required feedback. The first, and more common method, is the capacitance-bridge technique shown in Fig.11(a). The capacitance bridge becomes more apparent when the circuit is redrawn as shown in Fig.11(b). The condition for neutral-

Fig. 11 - Capacitance-bridge neutralization circuit: (a) actual circuit configuration; (b) circuit redrawn to emphasize capacitance-bridge network.

<sup>\*</sup> Conjugate match means that the transistor input and the generator and the transistor output and load are matched resistively and that all reactance is tuned out.

ization is that  $i_f = i_n$ . This condition implies the following relationship:

$$\frac{\mathbf{v_d}}{\mathbf{jX_f}} = \frac{-\mathbf{v_n}}{\mathbf{jX_n}}, \text{ or } \mathbf{C_f} \mathbf{v_d} = -\mathbf{C_n} \mathbf{v_n}$$

(4)

The voltage  $v_n$  is defined by the following equation:

$$\mathbf{v_n} = \left(\frac{\mathbf{v_d}}{\mathbf{jX_L} + \mathbf{jX_1}}\right) \mathbf{jX_1} = \left(\frac{\mathbf{v_d}}{\frac{\omega^2 \mathbf{LC_1} + \mathbf{1}}{\mathbf{j}\omega \mathbf{C_1}}}\right) \frac{1}{\mathbf{j}\omega \mathbf{C_1}} = \frac{\mathbf{v_d}}{-\omega^2 \mathbf{LC_1} + \mathbf{1}}$$

(5)

If this relationship for  $v_n$  is substituted in Eq.(4), the following result is obtained:

$$C_f v_d = -C_n \left( \frac{v_d}{-\omega^2 L C_1 + 1} \right)$$

, or  $C_n = -C_f (-\omega^2 L C_1 + 1)$  (6)

At resonance, the equation for the neutralization capacitance  $C_n$  may be rewritten as follows:

$$C_n = -C_f \left[ \left( \frac{-1}{\omega C_2} \right) \omega C_1 + 1 \right] = C_f \left( \frac{C_1}{C_2} - 1 \right)$$

(7)

If  $C_1 >> C_2$ , Eq.(7) may be rewritten as follows:

$$C_n \approx C_f \left(\frac{C_1}{C_2}\right)$$

(8)

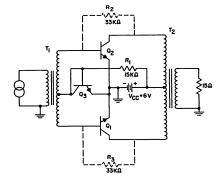

The other common method of neutralization is the transformer-coupled method shown in Fig.12. Again, the condition for neutralization is that  $i_{\rm f}=i_{\rm n}$ . The requirements for this condition are expressed by the following equation:

$$\frac{\mathbf{v_d}}{\mathbf{X_c}} = \frac{-\mathbf{v_n}}{\mathbf{X_n}}, \text{ or } \mathbf{C_f} \mathbf{v_d} = -\mathbf{C_n} \mathbf{v_n}$$

(9)

Fig. 12 - Transformer-coupled neutralization circuit.

Eq.(9) may be rewritten in the following form:

$$\left|\frac{\mathbf{v_d}}{\mathbf{v_n}}\right| = \frac{\mathbf{C_n}}{\mathbf{C_f}} \tag{10}$$

The required turns ratio for the coupling transformer can be determined from Eq. (10).

The generator and load impedances must be matched to the transistor input and output impedances, respectively, to obtain maximum gain. For the 200-MHz amplier shown in Fig.3, the generator resistance at the input is 50 ohms. For a conjugately matched input,

the generator admittance  $y_g$  and the real part of the transistor input admittance must appear to be equal. Because the generator admittance  $y_g$  is 20 mmhos and the real part of the input admittance  $Re\left(y_{11}\right)$  is 0.45 mmho, the coupling transformer must provide a transformation ratio of 44 to obtain the desired impedance match. The turns ratio required is determined as follows:

$$\frac{N_2}{N_1} = \sqrt{44} = 6.6$$

Experimentally, a turns ratio of 4 was found to be approximately the optimum value. This difference results, in part, from the fact that the parallel resistance of the tank coil was not considered in the calculation. At the output of the 200-MHz amplifier, the load is also 50 ohms. Because the dc drain voltage must be blocked from the load, a series matching capacitor was selected which performs both dc blocking and resistive matching simultaneously.

In the actual load-circuit network shown in Fig. 13(a), the value of capacitor  $C_8$  must be chosen so that the load admittance,  $y_L=20$  millimhos, is apparently equal to the real part of the transistor output admittance,  $Re(y_{22})=0.28$  millimhos. Fig. 13(b) shows the equivalent circuit of the load-circuit network for this condition.

Fig.13 - Output network in which series coupling capacitance is used for dc-voltage blocking and resistive matching: (a) actual network;

(b) electrical equivalent.

The following equation gives the input impedance  $\mathbf{Z}_{IN}$  for the network shown in Fig.13:

$$Z_{IN} = R_S + \frac{1}{i \omega C_S}$$

(11)

The input admittance  $y_{IN}$ , therefore, may be expressed as follows:

$$y_{IN} = \frac{1}{R_p} + j \omega C_p = \frac{1}{Z_{IN}} = \frac{1}{R_s + \frac{1}{j \omega C_s}}$$

(12)

The terms in Eq.(12) are rearranged to obtain the following result:

$$\frac{R_S}{R_p} + j \omega C_p R_S + \frac{1}{j \omega C_S R_p} + \frac{j \omega C_p}{j \omega C_S} = 1$$

(13)

The real and imaginary terms in Eq.(13) are equated to obtain the following relationships:

$$\frac{R_S}{R_p} + \frac{C_p}{C_S} = 1 \tag{14}$$

$$\omega C_p R_S - \frac{1}{\omega C_S R_p} = 0$$

(15)

$$C_{p} = \frac{1}{(\omega C_{S} R_{p})(\omega R_{S})}$$

(16)

Eq.(16) is substituted into Eq.(14) to obtain the following equation for the matching capacitance  $C_s$ :

$$C_{S} = \frac{1}{\omega} \sqrt{\frac{1}{(R_{n} - R_{s}) R_{s}}}$$

(17)

Substitution of numerical values for the parameters in Eq. (17) yields the following value for  $C_S$ :

$$C_S = \frac{1}{2\pi(2 \times 10^8)} \sqrt{\frac{1}{(3600 - 50)50}} = 1.9 \text{ pF}$$

Experimentally, a 3-picofarad capacitor was found to perform very satisfactorily in the amplifier. If  $R_p\!>\!>\!R_s$ , then  $C_p\approx C_s$ . Therefore, a 3-picofarad capacitance appears in parallel with the 1.4-picofarad capacitance of the MOS transistor. A small 1-to-9-picofarad variable air capacitor was selected for the tank tuning capacitor to compensate for variations among transistors. For a nominal value of 2 picofarads for the air capacitor, the total output capacitance is 6.4 picofarads. The inductance required to resonate with 6.4 picofarads at 200 MHz is 0.1 microhenry. When the total output capacitance is known, the required neutralization capacitor can be calculated. If  $C_1$  is arbitrarily selected as 33 picofarads, the neutralization is determined from Eq.(8),

as follows:

$$C_n \approx C_f \left(\frac{C_1}{C_2}\right) = 0.2 \left(\frac{33}{6.4}\right) = 1.0 \text{ pF}$$

The optimum value for the neutralization capacitor was determined experimentally by use of a small (0.5-to-3-picofarad) variable capacitor. This capacitor was adjusted to the optimum value for a typical unit ( $C_{rss}=0.13~pF$ ) and then fixed. The required input inductance was found to be 0.06 microhenry. The completed amplifier is shown schematically in Fig.3. The bandwidth of the amplifier is typically 8 MHz and shows negligible skew.

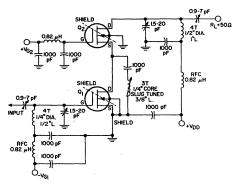

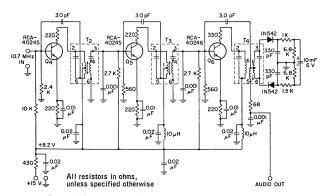

The y parameters may also be used to design a cascode vhf amplifier such as the one shown in Fig.5. This circuit had typical power gain and noise figure of 17 dB and 4.2 dB, respectively. The amplifier has a bandwidth of 10 MHz with negligible skew. The capacitance of the source<sub>2</sub>-drain<sub>1</sub> interconnection must be tuned out to achieve a good vhf noise figure. The noise figure of the cascode amplifier is 2 to 3 dB higher if this capacitance is not tuned out.

### References

- 1 Gerald Theriault, "Cross-Modulation and Modulation Distortion of RF Transistors," IRE Trans. on Broadcast and Television Receivers, July 1962.

- 2 J. G. Linvill and J. F. Gibbons, Transistors and Active Circuits, McGraw-Hill Book Co., Inc., New York, 1961.

- 3 A. P. Stern, "Stability and Power Gain of Tuned Transistor Amplifiers," Proceedings of the IRE, March 1957.

- 4 George D. Johnson, "High-Frequency Amplifier Design using Admittance Parameters," Electro-Technology, November 1963.

# **MOS Field-Effect Transistors**

Application Note

# VHF Mixer Design Using the RCA-3N128 MOS Transistor

Ьy

F. M. Carlson

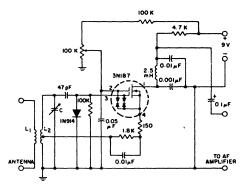

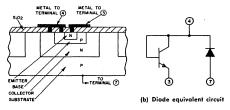

The 3N128 is a vhf MOS field-effect transistor suitable for use throughout the vhf band (30 to 300 MHz) as an amplifier, mixer, or oscillator. This Note discusses some of the design criteria pertinent to the construction of MOS mixers, and presents an example of a complete vhf MOS converter.

### Mixer Design Considerations

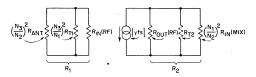

The conversion gain obtained from a mixer is the ratio of intermediate-frequency (if) power output divided by the radio-frequency (rf) power input. This conversion gain CG is usually expressed in dB, as follows:

$$CG = 10 \log \frac{if P_{out}}{rf P_{in}}$$

The value of CG approximates the gain of the active device operated as an amplifier (unneutralized) at the intermediate frequency, minus the rf losses at the input of the device. Practical mixers normally have a conversion gain of 3 to 5 dB less than their if-amplifier gain.

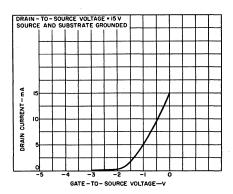

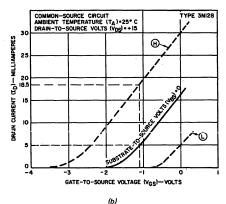

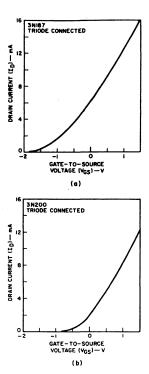

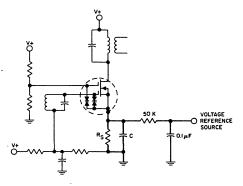

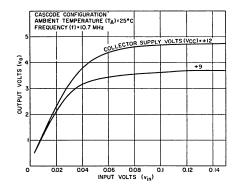

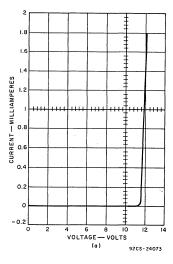

The 3N128 transistor has good gain and noise figure throughout the vhf band. Because it also has a nonlinear region of operation, it may be used as a vhf mixer to provide good conversion gain. The transfer function of the 3N128, shown in Fig.1, indicates that the maximum nonlinearities occur at a drain current of about 1.5 milliampere. At drain currents above approximately 5 milliamperes, the transfer function starts to become linear. No mixing action can occur if the transfer function is perfectly linear. Because the ampli-

fier gain of the 3N128 is higher at 5 milliamperes than at 1.5 milliamperes, the best bias point for an MOS mixer is a compromise between the region where best mixing occurs and the region where optimum if power gain occurs. For the 3N128, this point is empirically determined to be between 3.5 and 4.5 milliamperes.

Fig. 1 - Drain current as a function of gate-to-source voltage for the 3N128 vhf MOS transistor.

The local-oscillator signal may be introduced into a 3N128 mixer at the insulated gate, the source, or the junction gate (substrate). Application of the oscillator signal to the junction gate can be very effective, but is not recommended because the junction gate of the

3N128 is tied to the case; placing the transistor case at local-oscillator signal potential can pose possible radiation problems.

Injection of the oscillator signal at the source is not desirable because the source should always be at rf/if ground for optimum gain, but could not be at ground at the oscillator frequency. Designing a network to meet these criteria is difficult and adds to the cost of the mixer.

Injection of the oscillator signal at the insulated gate is the least troublesome of the three methods. The local oscillator may be coupled to the insulated gate by means of an inductive loop or a small coupling capacitor.

The input circuit is normally designed for a conjugate match with the input impedance of the MOS transistor at the radio frequency. The output circuit is normally designed for a conjugate match with the output impedance of the 3N128 at the intermediate frequency, unless electrical instabilities (oscillations) occur, in which case the output circuit must be mismatched. Oscillations are not normally a problem in a 3N128 mixer, provided the if and rf signals are relatively far apart in frequency. Under these conditions, the output circuit presents a low impedance to the rf signal, and the input circuit presents a low impedance to the if signal; consequently, oscillations at either frequency are unlikely to occur.

Neutralization is not generally used in mixers because of the different frequencies at the output and the input.

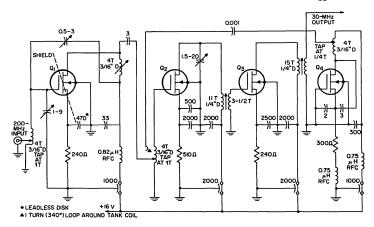

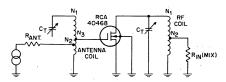

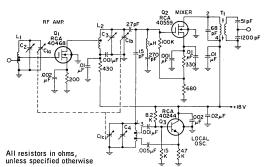

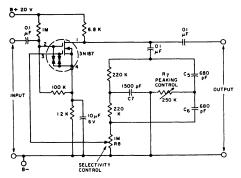

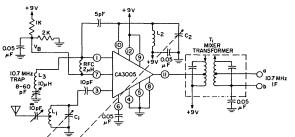

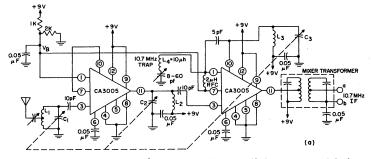

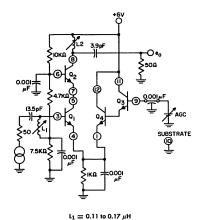

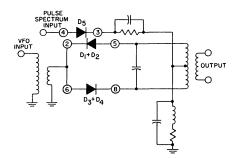

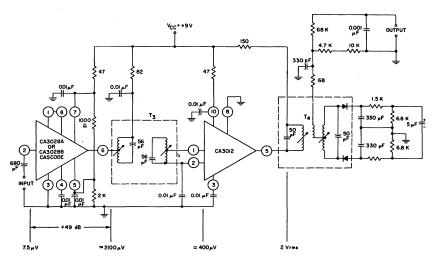

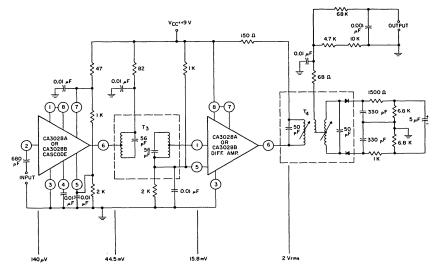

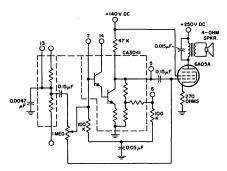

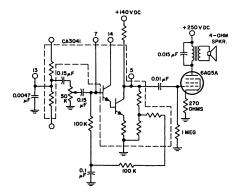

# Design Example

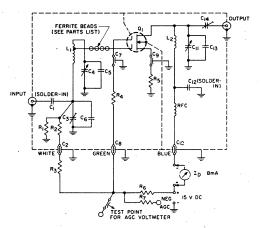

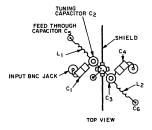

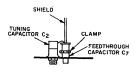

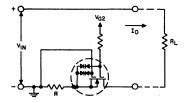

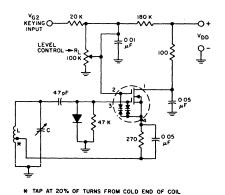

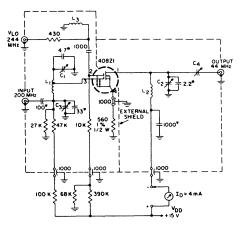

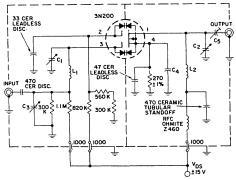

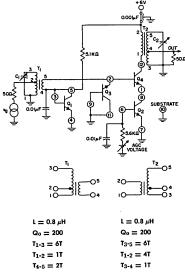

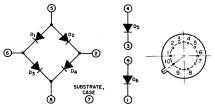

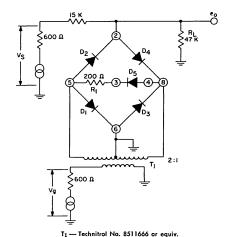

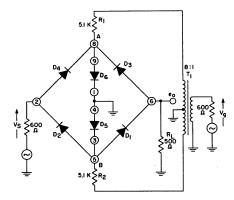

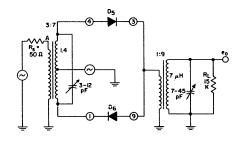

A vhf receiver "front end" has been designed and built to demonstrate the preceding design considerations and to illustrate the use of the 3N128 vhf MOS transistor in all four stages: rf, mixer, if, and local oscillator. The complete converter, shown in Fig.2, uses an rf input frequency of 200 MHz and an if output frequency of 30 MHz.

The input stage is a straight-through 200-MHz amplifier\* employing a source resistor for gate bias. This configuration permits the gate to be at dc ground, and greatly reduces the possibility of damage to the MOS gate from input transients. The 240-ohm resistor allows a current of approximately 5 milliamperes to flow through the device so that maximum vhf power gain is obtained. A variable inductor resonates with the output capacitance of the 3N128 to provide a bandwidth of approximately 12 MHz for the rf stage alone. (Narrower bandwidth could have been obtained by use of more capacitance in the tuned circuits and different loading on the output circuit; however, no particular effort was made to achieve very narrow bandwidth because a wide bandwidth is desirable in some applications.) Capacitive bridge neutralization is used to achieve the maximum allowable stage gain of 20 dB for the particular 3N128 used.

The input coil of the mixer stage is designed to permit a conjugate match with the transistor input admittance. The input admittance  $y_{11}$  of the 3N128 at 200 MHz is approximately 0.45 + j 7.2 millimhos. Therefore, an admittance of  $y_{11}^*$  (=0.45 - j 7.2 millimhos)

Fig. 2 - VHF receiver "front end" using the 3N128 in all stages.

<sup>\*</sup> Design information for vhf MOS amplifiers is given in RCA Application Note AN-3193: "Application Considerations for the RCA-3N128 VHF MOS Field-Effect Transistor," by F.M. Carlson, August 1966.

mhos) should be presented to the mixer input. A conjugate match is not used at the output because it is desirable to load the input of the following (if) stage for stability. Therefore, a step-down transformer is used. (A conjugate match would require use of a step-up transformer because  $g_{11} > g_{22}$  at 30 MHz.)

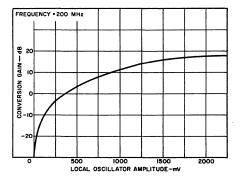

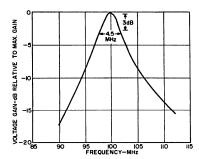

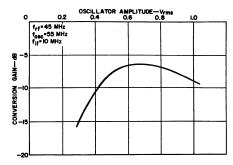

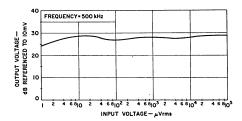

The local oscillator is coupled into the insulated gate of the mixer by means of an ungrounded 340-degree loop placed around the input tank coil at its high-impedance end. A small coupling capacitor could also be used for this purpose. Local-oscillator amplitude is approximately 1.4 volts rms into the coupling loop. Power gain of the mixer stage is 16 dB. Fig.3 shows the conversion gain of the mixer as a function of local-oscillator amplitude. A lower oscillator level than 1.1 volts would probably be desirable if spurious output frequencies were found to be troublesome.

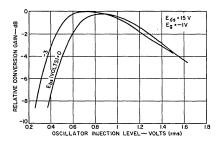

Fig.3 - Conversion gain of the mixer stage in Fig.2 as a function of local-oscillator amplitude.

A 510-ohm source resistor is used in the mixer stage to provide a drain current of 4 milliamperes. (This value is larger than would normally be expected for a drain current of this level because the gate is subjected to large signal excursions by the local oscillator.)

The maximum available gain (MAG) of the 3N128 at 30 MHz in a conjugately matched circuit (with y12

assumed to be approximately zero) may be computed from the y-parameters for the device, as follows:

MAG =

$$\frac{|y21|^2}{4 g_{11} g_{22}} = \frac{|7.2|^2}{4(0.03)(0.12)} = 3610 = 35.6 \text{ dB}$$

The maximum usable gain (MUG) of the 3N128 in an unneutralized 30-MHz amplifier is computed as follows:

$$\text{MUG} = \frac{0.4 \text{ gm}}{\omega C_{\text{TSS}}} = \frac{(0.4)(7.2)(10^{-3})}{(27)(30) \ 10^{6} \ (0.13) \ 10^{-12}} = 118 = 20.7 \ \text{dB}$$

If the 30-MHz stage is operated at a gain significantly above the MUG value, the possibility of circuit oscillation exists. Therefore, the input of the if stage is mismatched to reduce the stage gain from the MAG level to about 20 dB. (In some cases, it may be easier to mismatch at the output than at the input.) The output of the if stage is transformer-coupled to a 50-ohm load.

The local-oscillator stage is a Colpitts circuit in which frequency is adjusted by means of a slug-tuned inductor.

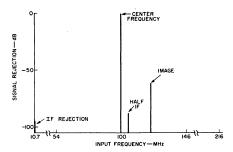

The complete converter has a power gain of 56 dB, a noise figure of 3 dB, and a bandwidth of 1.5 MHz. Spurious responses (referred to a level of 0 dB at the 200-MHz input frequency) are -51dB at 100 MHz, -36 dB at 215 MHz, and -35 dB at 260 MHz. These spurious responses could be greatly improved by use of a narrower bandwidth in the rf stage; the present bandwidth is 12 MHz at the 3-dB points.

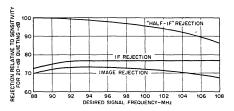

Table I shows measurements of cross-modulation of the converter as a function of frequency.

| Interfering | Interfering Signal Voltage Necessary |

|-------------|--------------------------------------|

| Frequency   | for 1% Cross-Modulation              |

| (MHz)       | (mV)                                 |

| 50          | 160                                  |

| 90          | 115                                  |

| 100         | 87                                   |

| 110         | 98                                   |

| 120         | 97                                   |

| 130         | 77                                   |

| 140         | 78                                   |

| 150         | 77                                   |

| 160         | 65                                   |

| 170         | 52                                   |

| 190         | 9                                    |

Table 1 - Cross-modulation of MOS mixer.

# **MOS Field-Effect Transistors**

Application Note AN-3452

# Chopper Circuits Using RCA MOS Field-Effect Transistors

ph.

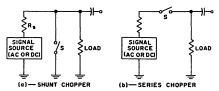

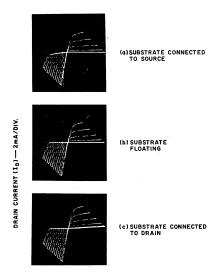

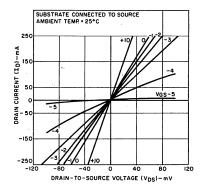

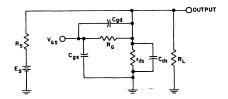

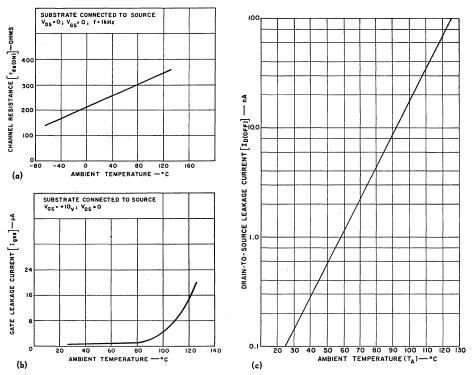

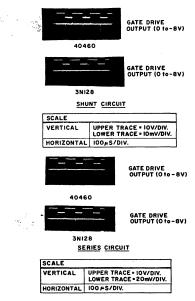

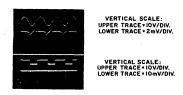

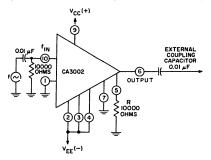

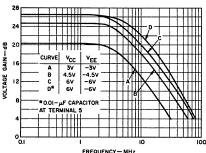

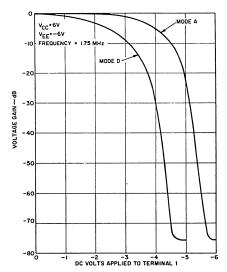

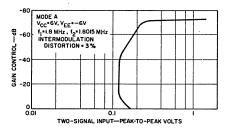

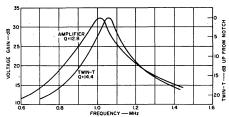

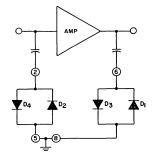

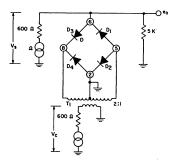

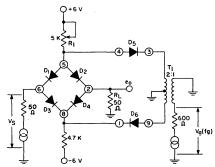

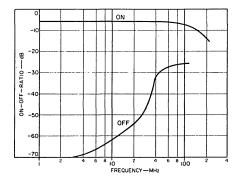

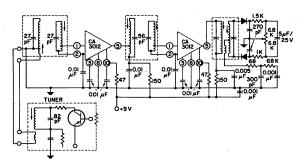

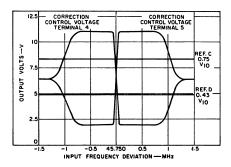

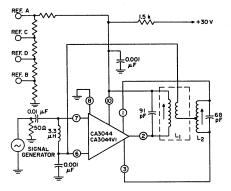

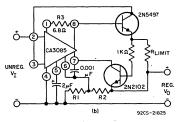

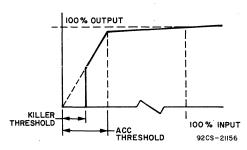

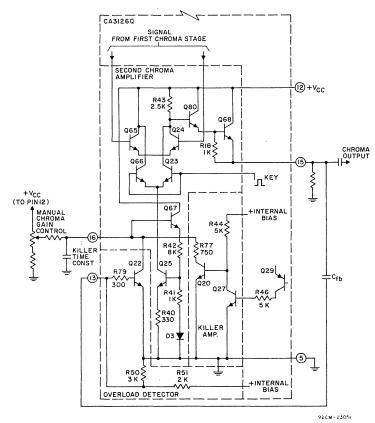

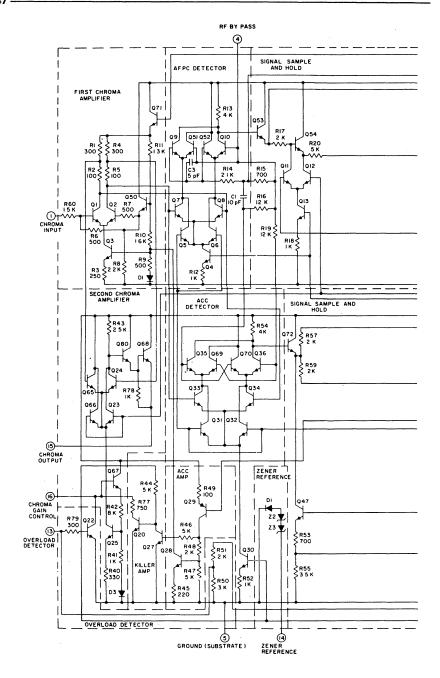

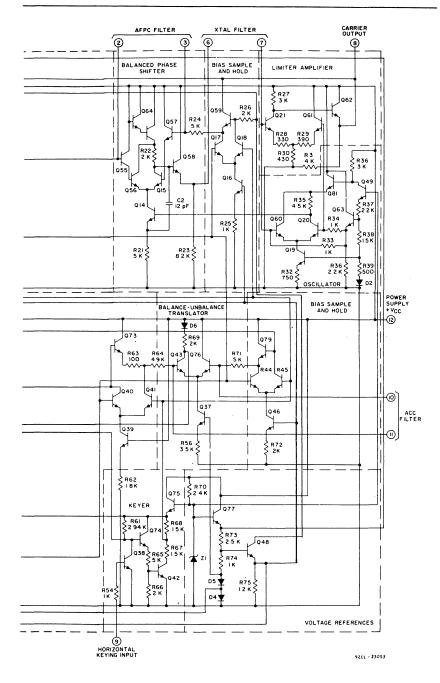

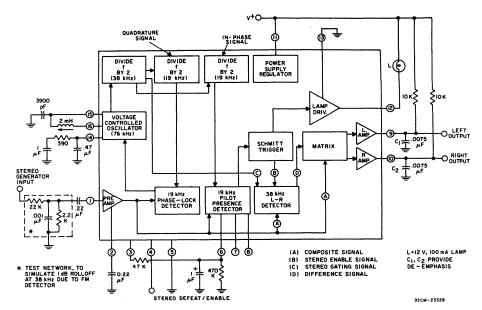

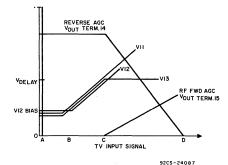

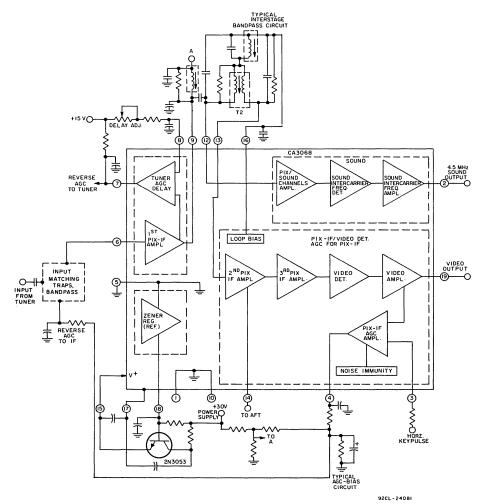

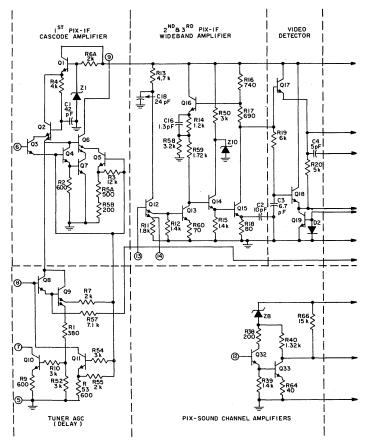

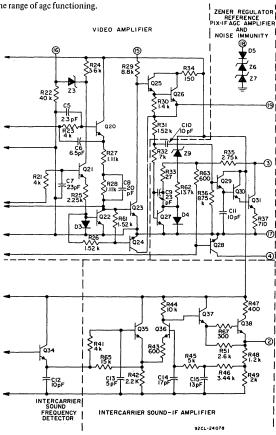

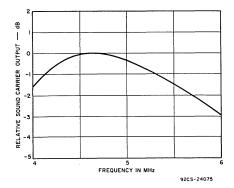

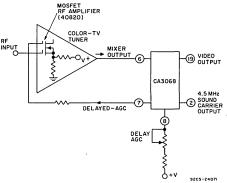

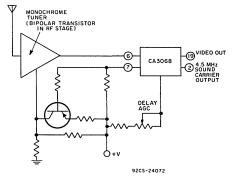

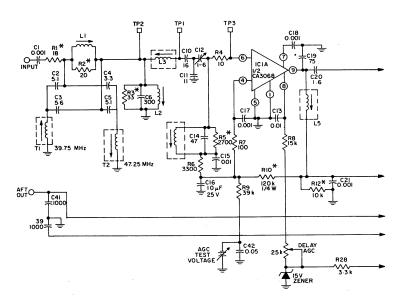

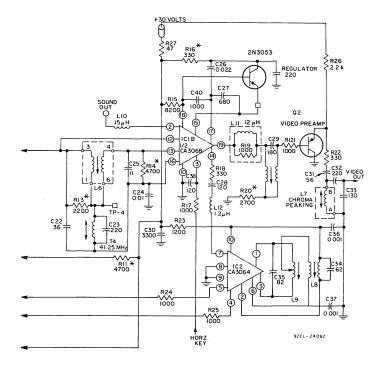

F. M. Carlson