# The Complete x86

The Definitive Guide to 386, 486, and Pentium-Class Microprocessors

**Volume I**

**Edited by John Wharton**

MICRODESIGN RESOURCES MicroDesign Resources 874 Gravenstein Hwy. So. Sebastopol, CA 95472 707.824.4004, fax: 707.823.0504

email: info@mdr.ziff.com

Copyright © 1994 MicroDesign Resources All rights reserved. Printed in the United States of America

ISBN 1-885330-02-2

No part of this report may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without prior written permission.

MicroDesign Resources is a trademark of Ziff-Davis Publishing L.P.

This report contains and analyzes information from publicly available sources and from industry contacts. Although we consider these sources reliable, we cannot guarantee the accuracy, whether past, present or future, of the information or analyses contained herein. Readers assume full responsibility for any use made of this report or its contents, in whole or in part.

Trademark names are used throughout this report. These trademarks are the property of their respective owners.

Please inform us of any errors of fact or omission so they may be corrected in future editions of the report.

### **Table of Contents**

|                | Forew     | ordxxxii:                                |

|----------------|-----------|------------------------------------------|

|                | Execu     | tive Summaryxxxv                         |

|                |           | Why this Report is Neededxxxv            |

|                | Prefac    | <b>Se</b> xxxvii                         |

|                |           | How this Report is Organizedxxxvii       |

|                |           | Terminologyxxxviii                       |

|                |           | Acknowledgments                          |

|                |           | Feedback and Updates                     |

|                | About     | the Authors xli                          |

|                | About     | the Publisher xliii                      |

| Volume I       |           |                                          |

| Part I: Prelim | inaries . |                                          |

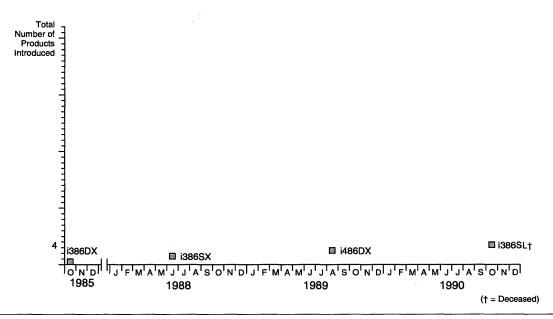

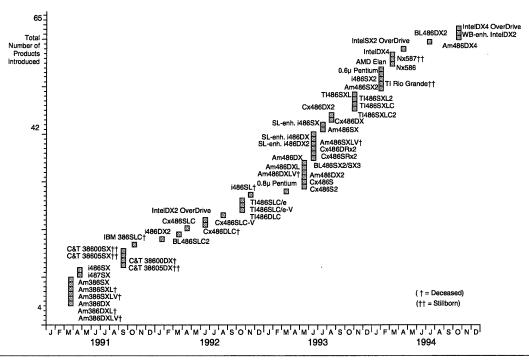

| •              | 1 The x8  | 36 Business Climate 3                    |

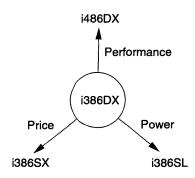

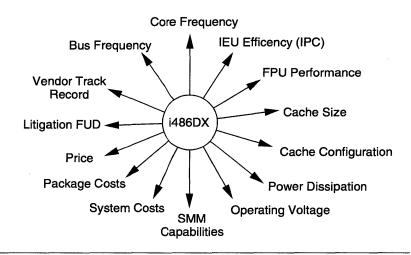

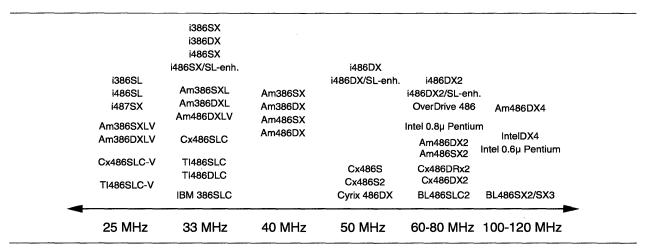

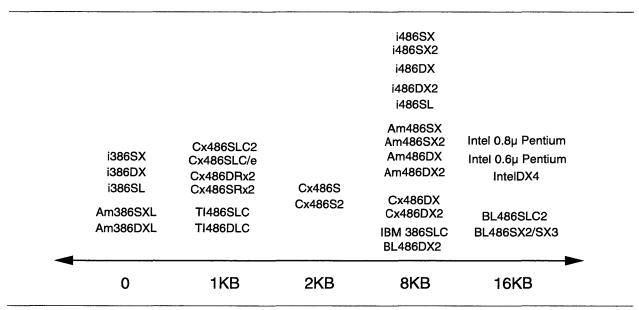

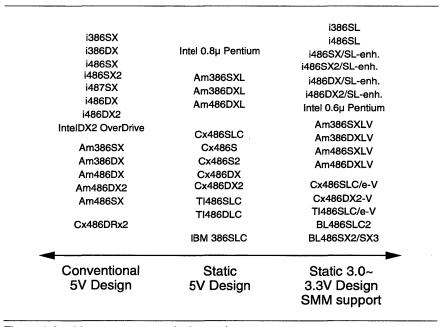

|                |           | The Explosion of Design Alternatives     |

|                |           | Forestalling the Blood Bath              |

|                |           | Dimensions of Differentiation            |

|                | 1.4       | Commentary                               |

|                |           | For More Information                     |

|                |           | Microprocessor Report Articles           |

|                |           | Other Technical References               |

|                |           | Other Periodicals                        |

| 2              | 2 x86 Fa  | ımily Heritage                           |

|                | 2.1       | Jurassic Parts                           |

|                |           | <i>The 8086</i> 19                       |

|                |           | The 8088 22                              |

|                |           | The 80186                                |

|                |           | The 80286                                |

|                | 2.2       | The 386 Family                           |

|                | 2.3       | The 486 Family                           |

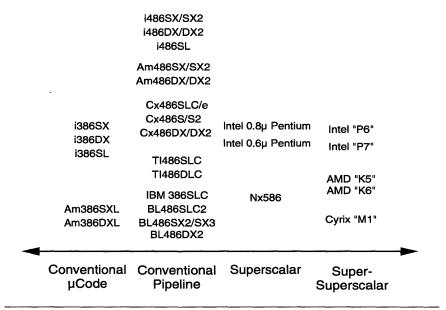

|                | 2.4       | The Explosion of Third-Party CPUs        |

|                |           | AMD Becomes an Industry Force            |

|                |           | Chips and Technologies Crashes and Burns |

|                |           | Cyrix Joins the Fray                     |

|                |           | TI Plays Copy Cat                        |

|                |           | IBM Pulls an End Run                     |

|                |           | Late Arrivals and Also-Rans              |

| 2.5                 | Intel Strikes Back                      | 30        |

|---------------------|-----------------------------------------|-----------|

|                     | "Second-Generation" 386 and 486 Designs | 30        |

| •                   | Pentium                                 | 31        |

| 2.6                 | Commentary                              | 32        |

|                     | The Intel Technology Treadmill          | 32        |

|                     | The Future of the x86 Market            | 33        |

| 2.7                 | For More Information                    | 34        |

|                     | Vendor Publications                     | 34        |

|                     | Microprocessor Report Articles          | 34        |

|                     | Other Technical References              | 34        |

| 3 The x8            | 36 Microprocessor Architecture          | 35        |

|                     | Common Ground                           |           |

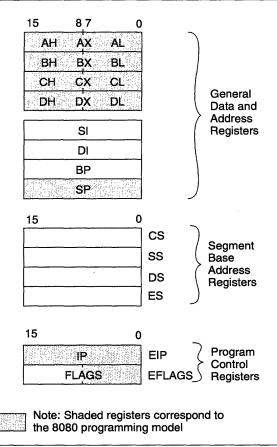

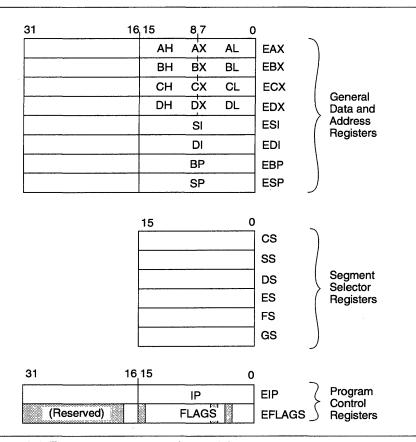

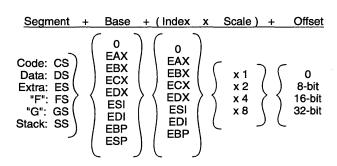

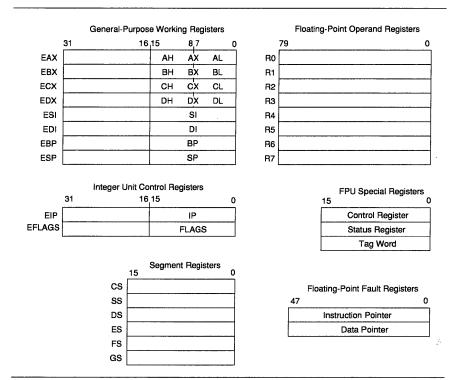

| 3.1                 | Programming Model                       | 36        |

|                     | Working Registers                       | 36        |

|                     | Program Control Registers               | 38        |

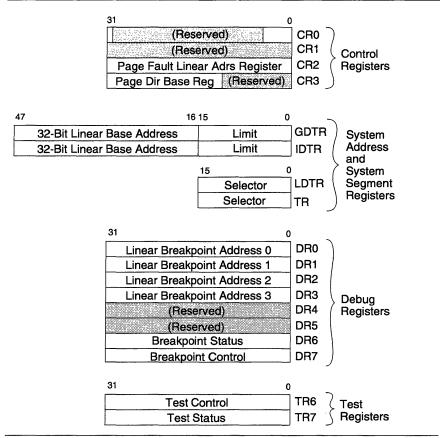

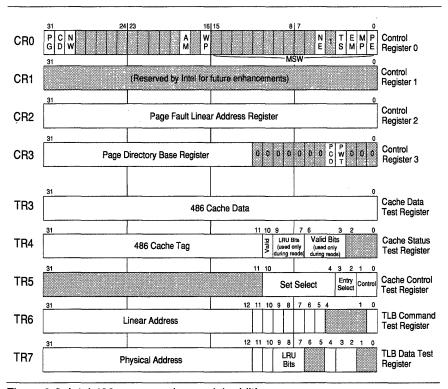

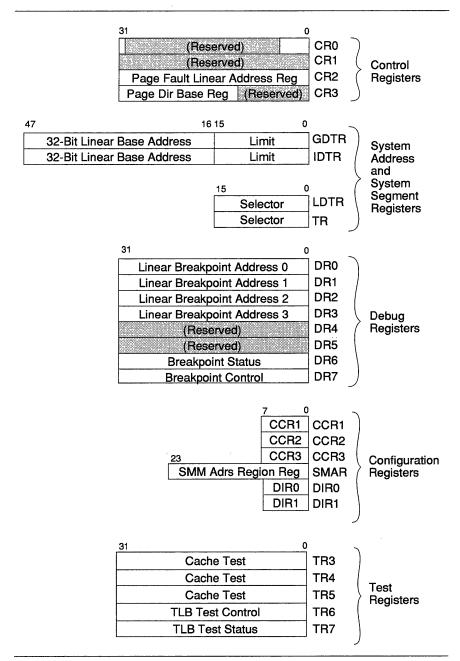

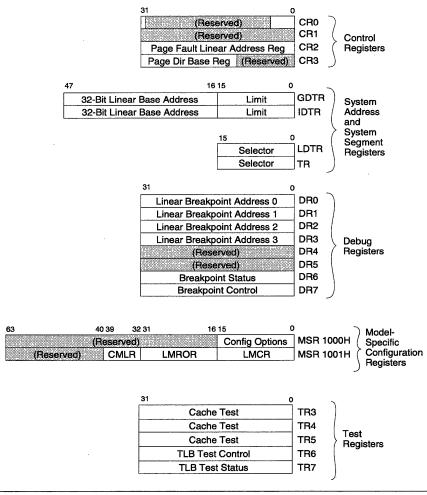

|                     | System Registers                        | 39        |

|                     | Control Register Functions              | 40        |

|                     | Breakpoint Registers                    | 41        |

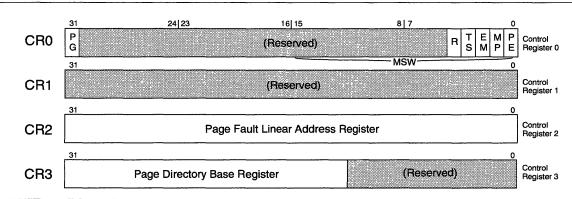

| 3.2                 | Integer Instructions                    | 41        |

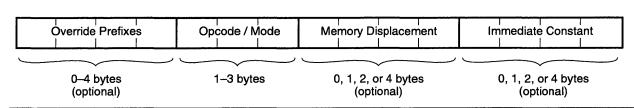

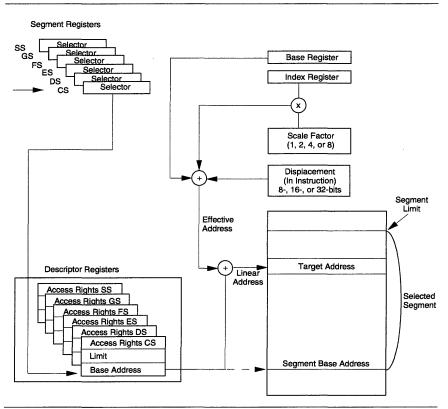

|                     | Memory Addressing                       | 43        |

|                     | Segmentation                            | 44        |

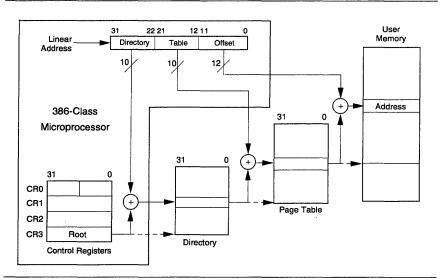

|                     | Memory Paging                           | 46        |

| 3.3                 | Floating-Point Architecture             | 47        |

|                     | FPU Instruction Set                     |           |

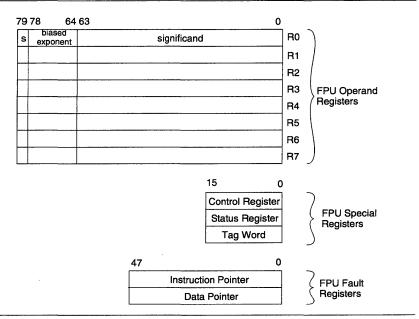

|                     | FPU Operand Registers                   | 49        |

|                     | FPU Control and Status Registers        | 50        |

|                     | FPU Exception and Trace Registers       | 50        |

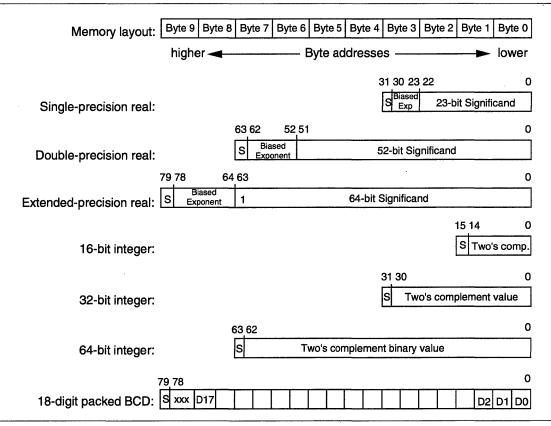

|                     | FPU Memory-Based Data Formats           | 50        |

| 3.4                 | CPU Operating Modes                     | 52        |

|                     | Interrupt and Exception Processing      |           |

| 3.5                 | For More Information                    | 53        |

|                     | Vendor Publications                     |           |

|                     | Microprocessor Report Articles          | 53        |

|                     | Other Technical References              | 54        |

| Double The Discour  |                                         |           |

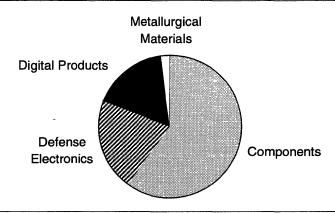

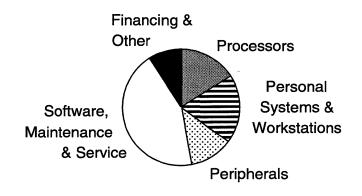

| rantii: The Players |                                         | 55        |

|                     | r Profiles                              |           |

|                     | Intel                                   |           |

|                     | Advanced Micro Devices                  |           |

|                     | Chips and Technologies                  |           |

|                     | Cyrix                                   |           |

| 4.5                 | Texas Instruments                       | <b>72</b> |

| 4.6                    | IBM                                        | 76  |

|------------------------|--------------------------------------------|-----|

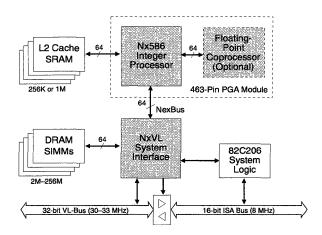

| 4.7                    | NexGen                                     | 79  |

| 4.8                    | For More Information                       | 80  |

|                        | Vendor Publications                        | 80  |

|                        | Microprocessor Report Articles             | 80  |

|                        | Other Technical References                 | 81  |

|                        | Other Periodicals                          | 81  |

|                        |                                            |     |

| Part III: The Products |                                            | 83  |

| 5 Intel 3              | 86 Microprocessors                         | 85  |

|                        | Intel 386 Family Overview                  | 85  |

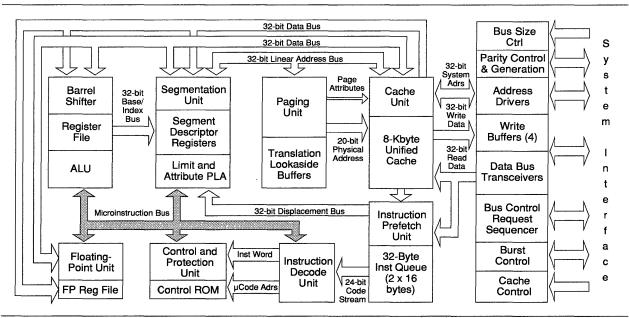

| 5.1                    | Intel 386 Core Technology                  | 86  |

|                        | Core Design                                | 87  |

|                        | Low-Level Instruction Timing               | 88  |

|                        | Clock Timing                               | 89  |

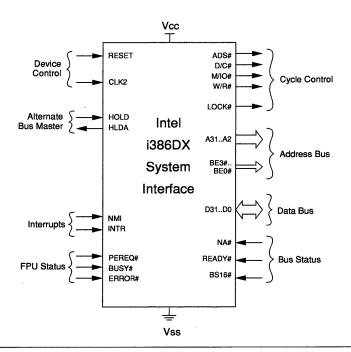

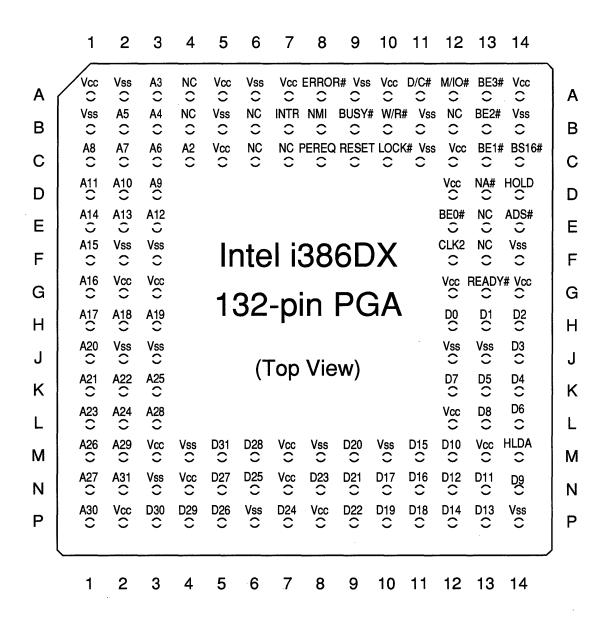

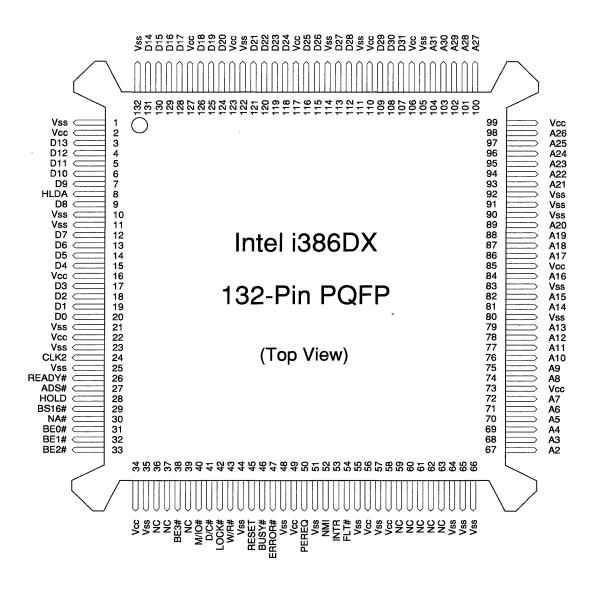

| 5.2                    | The Intel i386DX Microprocessor            | 90  |

|                        | Features                                   | 90  |

|                        | Cache Support                              | 91  |

|                        | Floating-Point Support                     | 91  |

|                        | System Interface                           | 91  |

|                        | Package and Frequency Options              | 95  |

|                        | Vital Statistics                           | 95  |

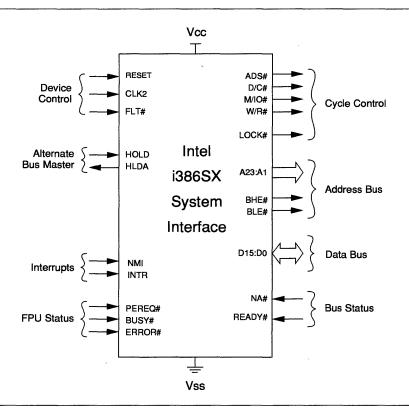

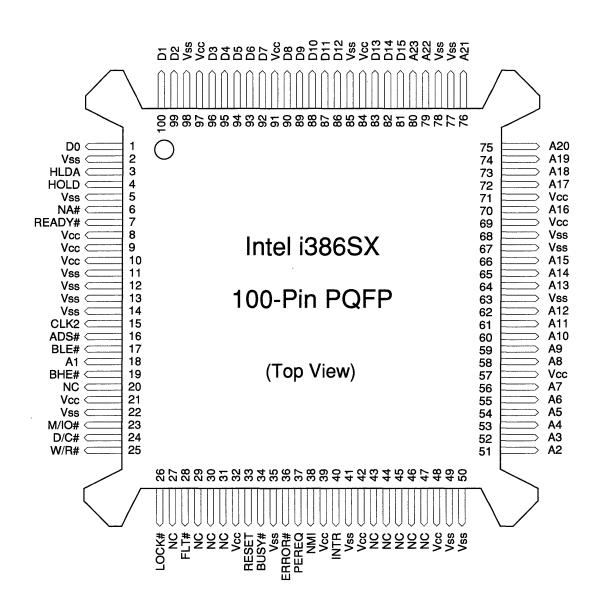

| 5.3                    | The Intel i386SX Microprocessor.           | 98  |

|                        | Background                                 | 98  |

|                        | Features                                   | 99  |

|                        | Cache Support                              | 100 |

|                        | Coprocessor Support                        | 101 |

|                        | System Interface                           |     |

|                        | Package and Frequency Options              | 102 |

| 5.4                    | The Intel 80376 Microprocessor             | 104 |

|                        | Background                                 | 104 |

|                        | Features                                   |     |

|                        | Architecture Modifications                 |     |

|                        | Package and Frequency Options              |     |

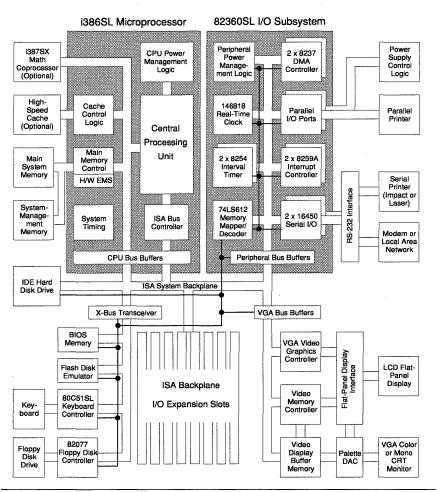

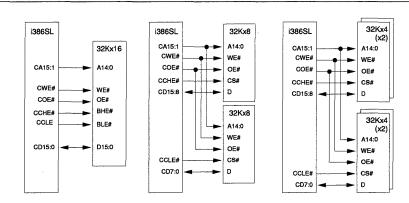

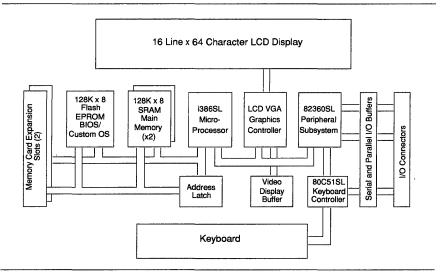

| 5.5                    | The Intel i386SL "SuperSet" Microprocessor |     |

|                        | Features                                   |     |

|                        | System Overview                            |     |

|                        | Cache Support                              |     |

|                        | Floating-Point Support                     |     |

| ,                      | System Interface Description               |     |

|                        | Package and Frequency Options              |     |

| 5.6                    | Futures                                    | 112 |

|   |         | Geopolitical Pawns?                             | 112 |

|---|---------|-------------------------------------------------|-----|

|   | 5.7     | For More Information                            | 113 |

|   |         | Vendor Publications                             | 113 |

|   |         | Microprocessor Report Articles                  | 113 |

|   |         | Other Technical References                      | 114 |

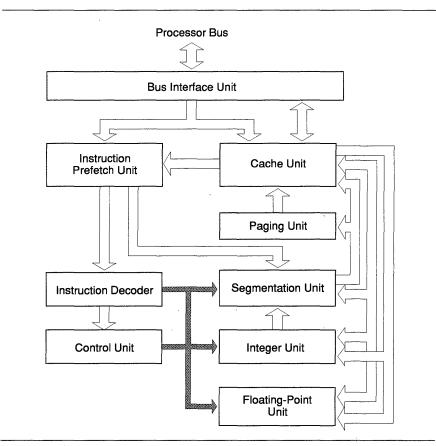

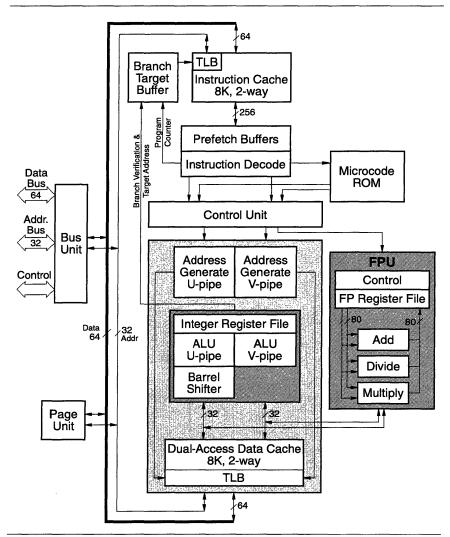

| 6 | Intel 4 | 86 Microprocessors                              | 117 |

|   |         | Intel 486 Family Overview                       | 117 |

|   |         | Architecture Extensions                         | 118 |

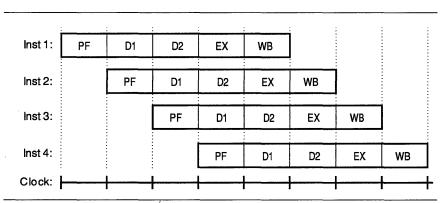

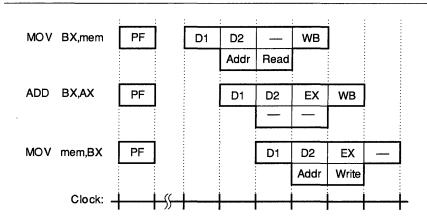

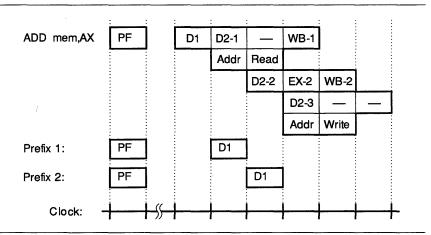

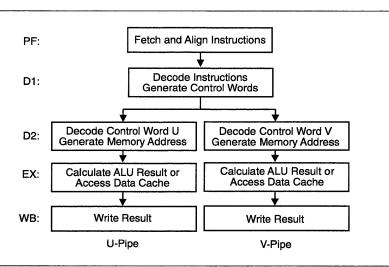

|   |         | Execution Pipeline                              | 121 |

|   |         | Instruction / Data Cache                        | 127 |

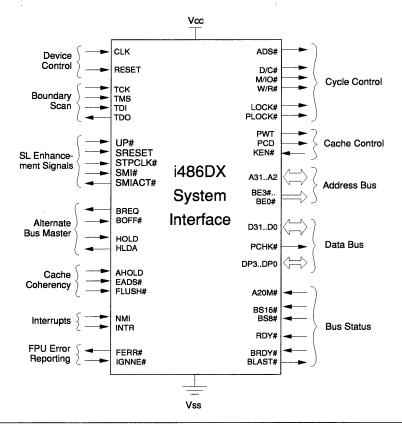

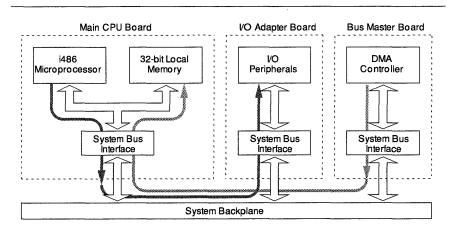

|   |         | System Interface                                | 130 |

|   |         | "SL-Enhanced" Processors                        | 133 |

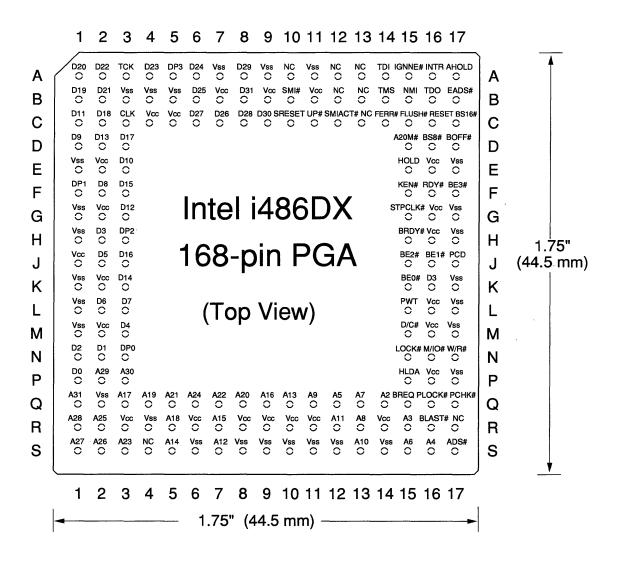

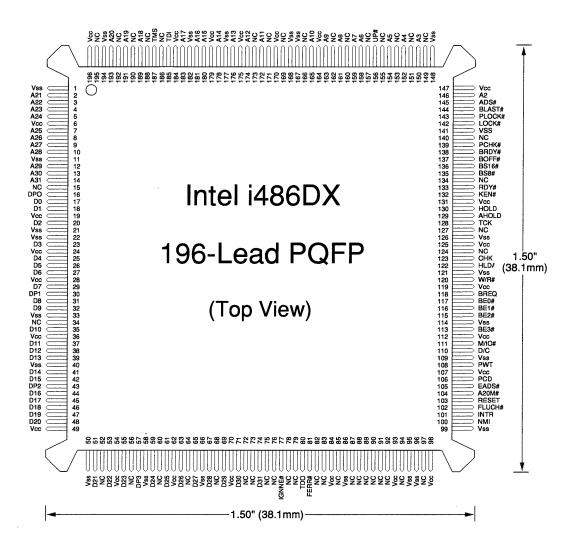

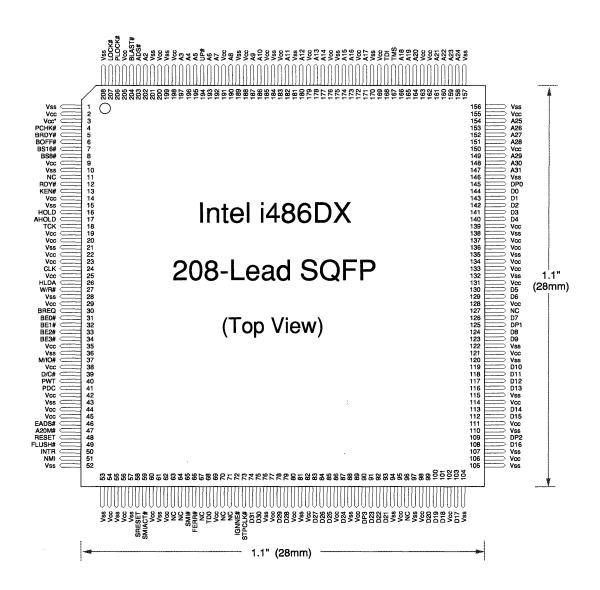

|   | 6.1     | The Intel i486DX Microprocessor                 | 135 |

|   |         | Floating-Point Unit                             | 136 |

|   |         | Processor Clock                                 | 136 |

|   |         | System Interface                                | 137 |

|   |         | Deadlock Backoff                                | 141 |

|   |         | SL-Enhancements                                 | 142 |

|   |         | Vital Statistics                                | 142 |

|   | 6.2     | The Intel i486DX-50 Microprocessor              | 147 |

|   |         | Background                                      | 147 |

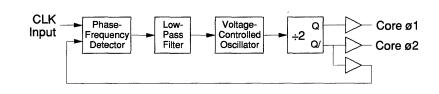

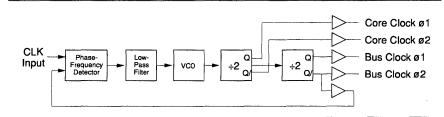

|   |         | Clock Synthesis Circuit                         | 148 |

|   |         | System Interface                                | 149 |

|   |         | Vital Statistics                                | 149 |

|   | 6.3     | The Intel i486DX2 Microprocessor                | 150 |

|   |         | Clock-Doubler Circuitry                         | 151 |

|   |         | Relative Performance                            | 152 |

|   |         | System Upgrade Good News/Bad News               | 152 |

|   |         | System Interface                                | 153 |

|   |         | Vital Statistics                                | 153 |

|   | 6.4     | The Write-Back-Enhanced IntelDX2 Microprocessor |     |

|   |         | Overview                                        | 154 |

|   |         | System Interface                                |     |

|   |         | Performance                                     | 156 |

|   | 6.5     | The IntelDX4 Microprocessor                     |     |

|   |         | Clock-Multiplier Options                        | 158 |

|   |         | Other Enhancements                              |     |

|   |         | System Interface                                | 159 |

|   |         | Vital Statistics                                |     |

|   | 6.6     | The Intel i486SX Microprocessor                 |     |

|   |         | System Interface                                | 162 |

|   |         | Relative Performance                            |     |

|   |         | Vital Statistics                                | 164 |

| 6.7   | The Intel i486SX2 Microprocessor             | . 165 |

|-------|----------------------------------------------|-------|

|       | Vital Statistics                             | . 165 |

| 6.8   |                                              |       |

|       | Features                                     | . 166 |

|       | System Interface                             |       |

|       | Vital Statistics                             | . 167 |

| 6.9   | The IntelDX2 OverDrive Microprocessor        |       |

|       | Features                                     |       |

|       | Pinout                                       |       |

|       | Vital Statistics                             |       |

| 6.10  | The IntelDX4 OverDrive Microprocessor        | . 171 |

| 6.11  | The IntelSX2 OverDrive Microprocessor        | . 172 |

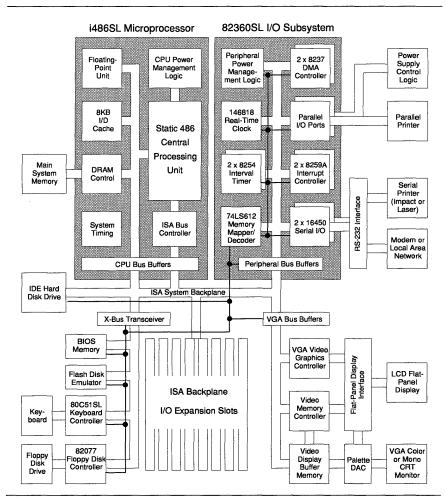

| 6.12  | The Intel i486SL Microprocessor.             | . 173 |

|       | Background                                   |       |

|       | "The Best Laid Plans"                        |       |

|       | Vital Statistics                             |       |

| 6.13  | The Intel "RapidCAD" 386 Microprocessor      |       |

|       | Features                                     |       |

|       | Vital Statistics                             | . 178 |

| 6.14  | Futures                                      |       |

|       | The "P24T"                                   | . 179 |

| 6.15  | Commentary                                   |       |

| 6.16  | For More Information                         |       |

|       | Vendor Publications                          |       |

|       | Microprocessor Report Articles               | . 182 |

|       | Other Technical References                   |       |

|       | Other Periodicals                            | . 185 |

| AMD 3 | 886 and 486 Microprocessors                  | 107   |

| AIIID | Background                                   |       |

| 7 1   | Core Design.                                 |       |

| •••   | Design Methodology                           |       |

|       | Compatibility and Performance                |       |

|       | Availability                                 |       |

| 7.2   |                                              |       |

|       | Features                                     |       |

|       | System Interface                             |       |

|       | Vital Statistics.                            |       |

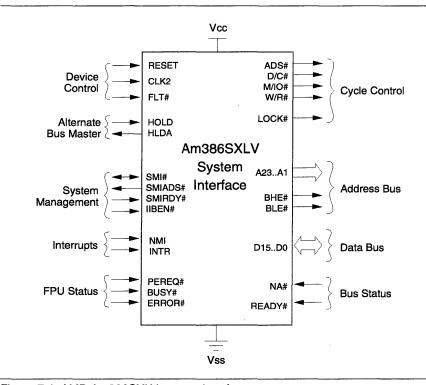

| 7.3   | The AMD Am386SXLV Microprocessor.            |       |

|       | Architecture Extensions                      |       |

|       | System Interface                             |       |

|       | Vital Statistics.                            |       |

| 7.4   | The AMD Am386DX and Am386DXL Microprocessors |       |

| •••   | System Interface                             |       |

|       |                                              |       |

7

8

|       | Vital Statistics.                              | 199 |

|-------|------------------------------------------------|-----|

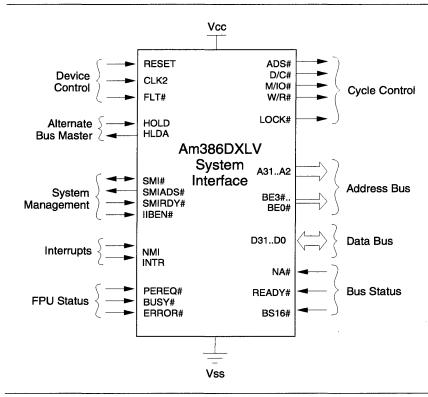

| 7.5   | The AMD Am386DXLV Microprocessor               |     |

| 1.0   | Features                                       |     |

|       | Vital Statistics.                              |     |

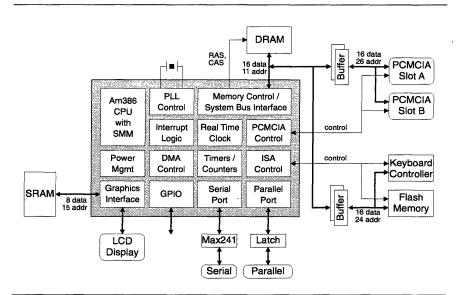

| 7.6   | The AMD Am386SC300 "Elan" Microprocessor       |     |

| 1.0   | Features                                       |     |

|       | System Interface                               |     |

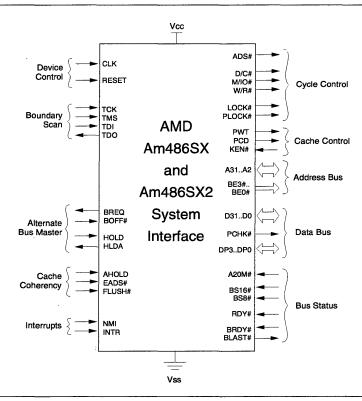

| 7.7   | The AMD Am486SX and Am486SX2 Microprocessors   |     |

| •••   | System Interface                               |     |

| *     | Vital Statistics.                              |     |

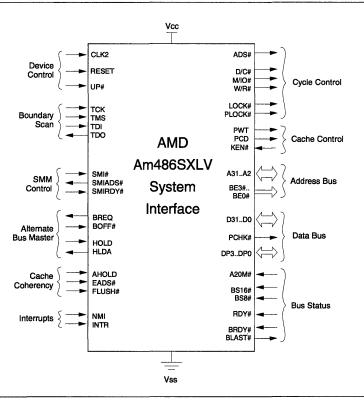

| 7.8   | The AMD Am486SXLV Microprocessor               |     |

|       | Architecture Extensions                        |     |

|       | System Interface                               |     |

|       | Vital Statistics.                              |     |

| 7.9   | The AMD Am486DX Microprocessor                 |     |

|       | Vital Statistics                               |     |

| 7.10  | The AMD Am486DX2 Microprocessor                |     |

|       | Features                                       |     |

|       | Vital Statistics                               |     |

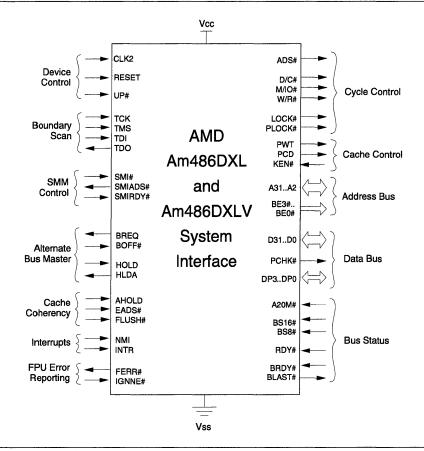

| 7.11  | The AMD Am486DXL and Am486DXLV Microprocessors |     |

|       | System Interface                               |     |

|       | Vital Statistics                               | 215 |

| 7.12  | The AMD Am486DX4 Microprocessor                | 216 |

| 7.13  | Futures                                        |     |

| 7.14  | Commentary                                     |     |

|       | Technical Comparisons                          | 219 |

|       | Legal Entanglements                            | 219 |

|       | Business Strategy                              | 221 |

|       | Production Limitations                         | 222 |

| 7.15  | For More Information                           | 223 |

|       | Vendor Publications                            | 223 |

|       | Microprocessor Report Articles                 | 224 |

|       | Other Technical References                     | 226 |

|       | Other Periodicals                              | 226 |

|       |                                                |     |

| C&I 3 | 86 Microprocessors                             |     |

|       | Overview                                       |     |

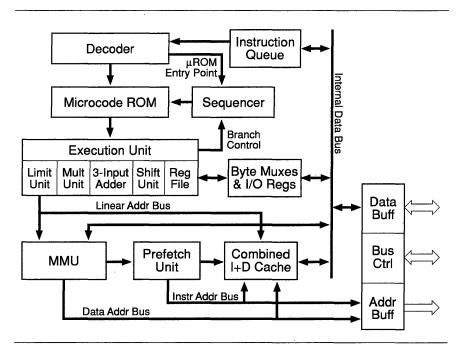

| 0.1   | Core Design                                    |     |

| 8.1   | The C&T 38600DX Microprocessor                 |     |

|       | System Interface                               |     |

|       | Package and Frequency Options                  |     |

| 0.0   | Relative Performance                           |     |

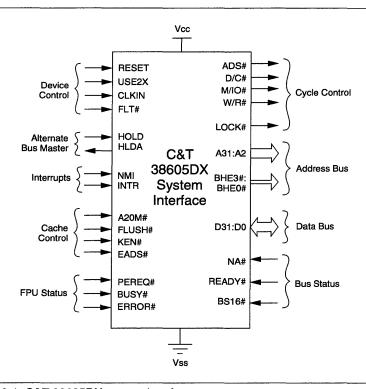

| 8.2   | The C&T 38605DX Microprocessor                 |     |

|       | Cache Design                                   | 232 |

|   |         | System Interface                             | 233   |

|---|---------|----------------------------------------------|-------|

|   |         | Relative Performance                         | 234   |

|   | 8.3     | Commentary                                   | 235   |

|   |         | Too Little, Too Different, Too Late?         | 235   |

|   | 8.4     | For More Information                         | 236   |

|   |         | Vendor Publications                          | 237   |

|   |         | Microprocessor Report Articles               | 237   |

| ^ | Chamina | AGC Micropycocococ                           | 000   |

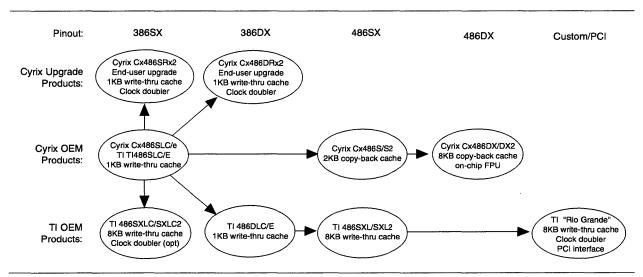

| 9 |         | 486 Microprocessors                          |       |

|   | 9.1     | Core Design.                                 |       |

|   |         | Pipeline Performance                         |       |

|   |         | Architecture Enhancements                    |       |

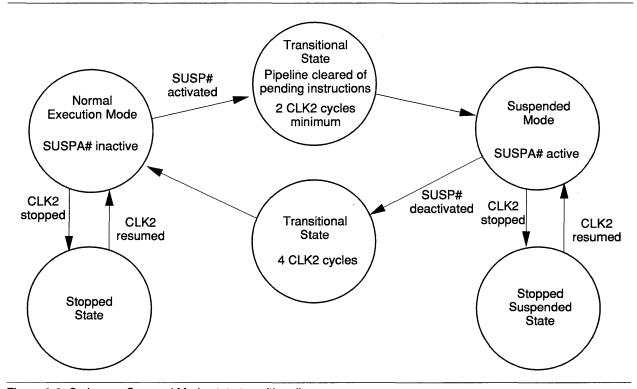

|   | 0.0     | System Management and Standby Modes          |       |

|   | 9.2     |                                              |       |

|   |         | Features                                     |       |

|   |         | Cache Configuration                          |       |

|   | *       | Instruction Set Additions                    |       |

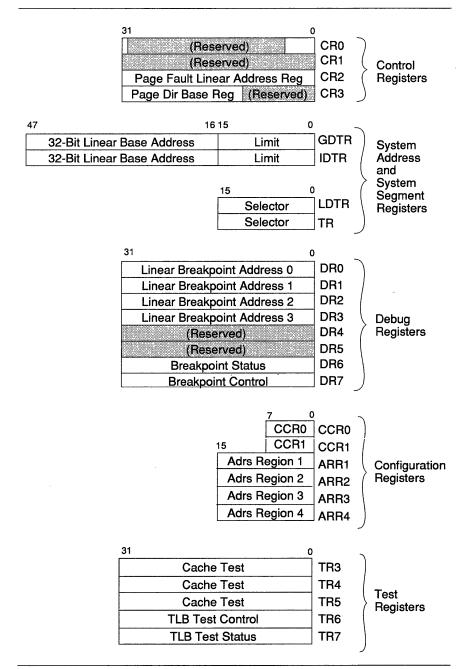

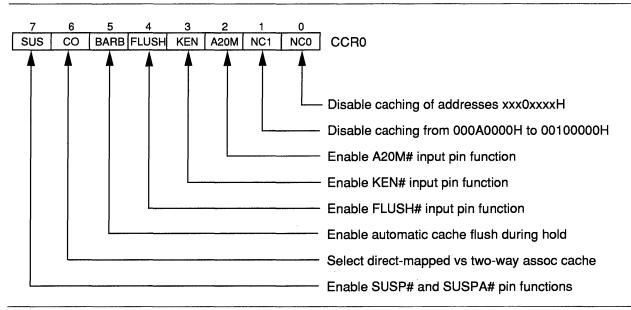

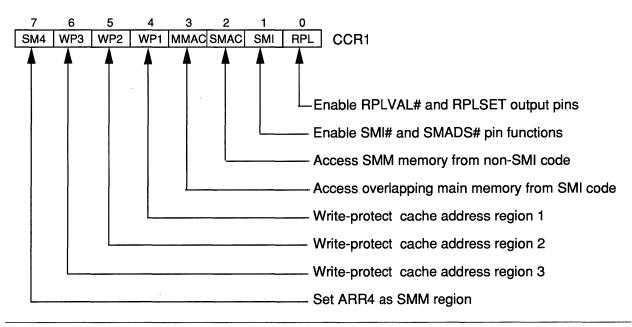

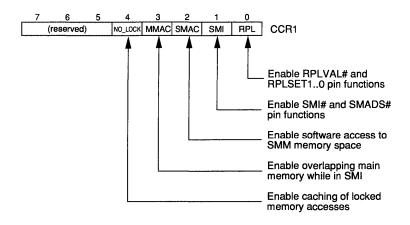

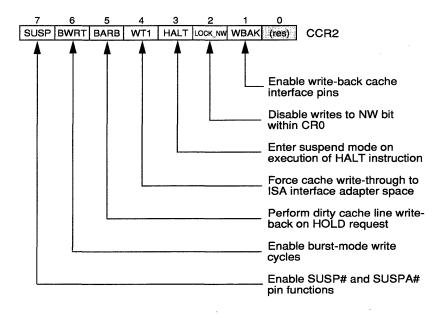

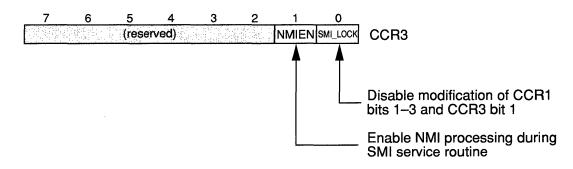

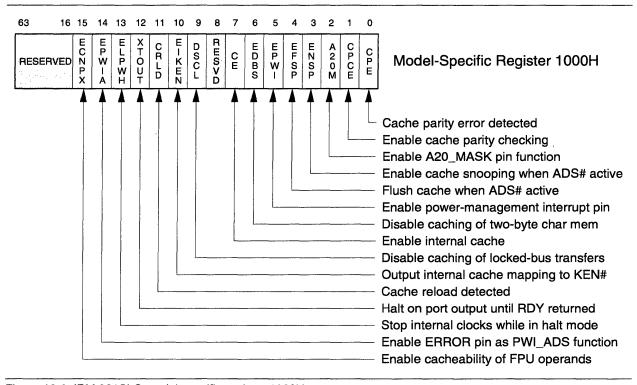

|   |         | Configuration Registers                      |       |

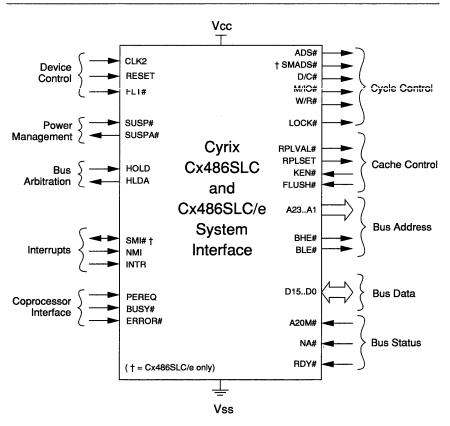

|   |         | System Interface                             |       |

|   |         | Clocking Regimes                             |       |

|   |         | Relative Performance                         |       |

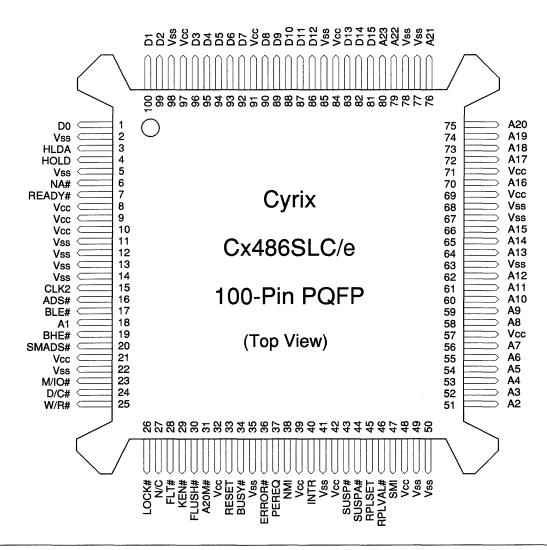

|   |         | Package and Pinout                           |       |

|   |         | Vital Statistics                             | . 255 |

|   | 9.3     | The Cyrix Cx486SLC/e-V Microprocessor        | . 257 |

|   |         | Vital Statistics                             | . 257 |

|   | 9.4     | The Cyrix Cx486SLC2 Microprocessors          |       |

|   |         | Vital Statistics                             | . 258 |

|   | 9.5     | The Cyrix Cx486DLC Microprocessor            | . 259 |

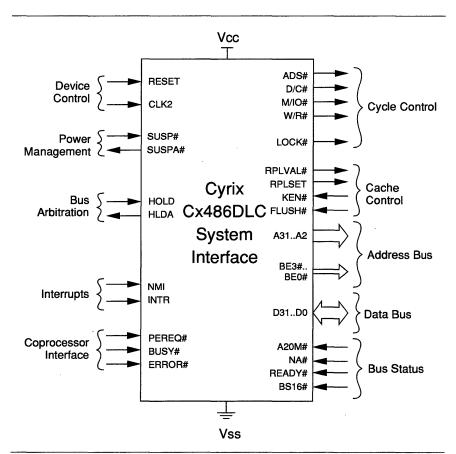

|   |         | System Interface                             | . 259 |

|   |         | Relative Performance                         | . 260 |

|   |         | Mortal Statistics                            | . 261 |

|   | 9.6     | The Cyrix Cx486SRx2 Microprocessor           | . 262 |

|   |         | Product Overview                             | . 263 |

|   |         | Frequency Options                            | . 264 |

|   | 9.7     | The Cyrix Cx486DRx2 Microprocessor           | . 265 |

|   |         | Frequency Options                            | . 266 |

|   | 9.8     | The Cyrix Cx486S and Cx486S2 Microprocessors | . 267 |

|   |         | Cache Characteristics                        | . 268 |

|   |         | Floating-Point Strategy                      | . 268 |

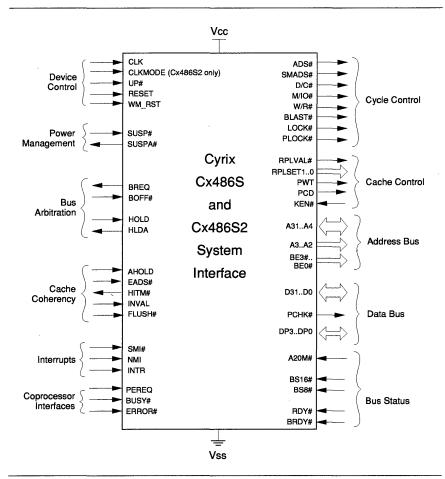

|   |         | System Interface                             | . 269 |

|   |         | Clocking Regimes                             | . 272 |

|   |         | Instruction Set Additions                    |       |

|   |         | Configuration Registers                      | . 273 |

|   |         | Vital Statistics                             | 276   |

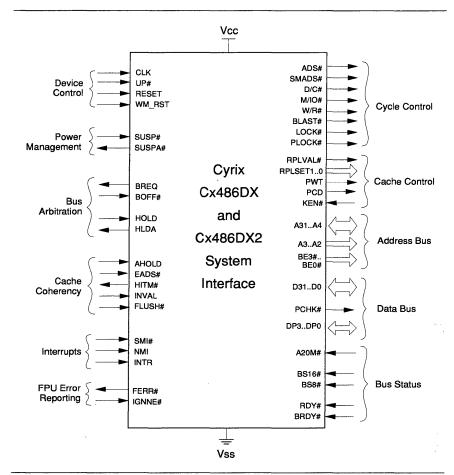

|    | 9.9    | The Cyrix Cx486DX and Cx486DX2 Microprocessors       | 277 |

|----|--------|------------------------------------------------------|-----|

|    |        | Cache Design                                         | 278 |

|    |        | Floating-Point Unit 2                                | 278 |

|    |        | System Interface                                     | 279 |

|    |        | Power Management 2                                   | 279 |

|    |        | Relative Performance                                 | 280 |

|    |        | Vital Statistics 2                                   | 280 |

|    | 9.10   | Commentary                                           | 282 |

|    |        | What's in a Name? 2                                  | 282 |

|    |        | Business Issues                                      | 283 |

|    |        | Legal Issues                                         | 284 |

|    |        | Compatibility 2                                      | 284 |

|    | 9.11   | For More Information                                 | 285 |

|    |        | Vendor Publications                                  | 285 |

|    |        | Microprocessor Report Articles                       | 285 |

|    |        |                                                      |     |

| 10 | IBM 38 | 36 and 486 Microprocessors 2                         | 287 |

|    |        | Dysfunctional Corporate Relations                    | 287 |

|    |        | Creatively Licensed                                  |     |

|    |        | Competitive Thrusts                                  | 289 |

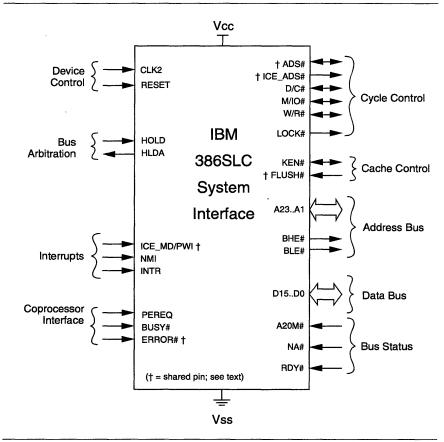

|    | 10.1   | The IBM 386SLC Microprocessor                        | 290 |

|    |        | Cache Configuration                                  | 291 |

|    |        | System Interface 2                                   |     |

|    |        | Programming Model Extensions 2                       | 296 |

|    |        | Instruction Set Extensions                           | 298 |

|    |        | Vital Statistics 2                                   | 299 |

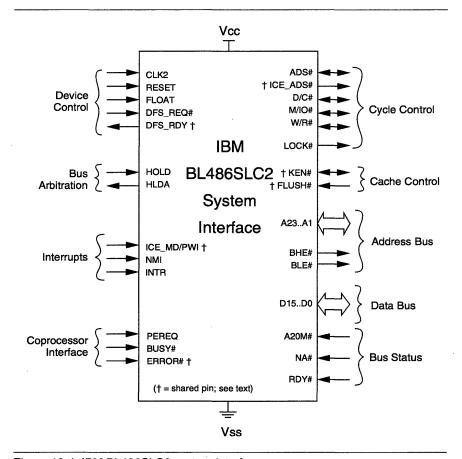

|    | 10.2   | The IBM BL486SLC2 Microprocessor                     | 300 |

|    |        | Cache Configuration                                  | 300 |

|    |        | Clocking Regimes 3                                   | 301 |

|    |        | System Interface 3                                   | 301 |

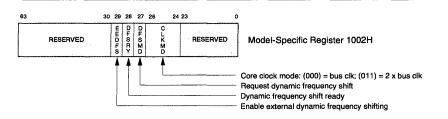

|    |        | Architecture Extensions                              | 303 |

|    |        | Vital Statistics 3                                   |     |

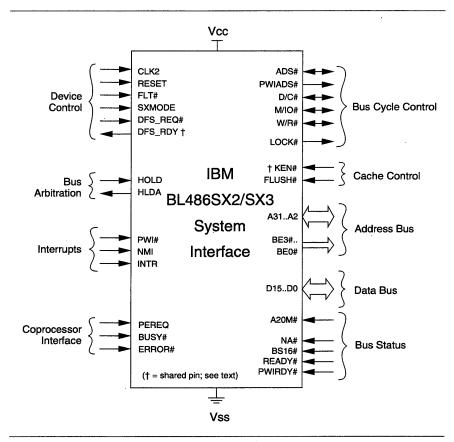

|    | 10.3   | The IBM BL486SX2/SX3 "Blue Lightning" Microprocessor | 05  |

|    |        | System Interface 3                                   | 306 |

|    |        | Vital Statistics 3                                   | 306 |

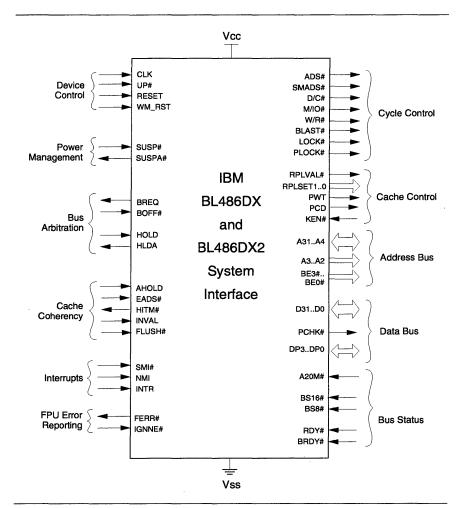

|    | 10.4   | The IBM BL486DX and BL486DX2 Microprocessors         |     |

|    |        | System Interface 3                                   | 309 |

|    |        | Vital Statistics 3                                   | 310 |

|    | 10.5   | Futures 3                                            | 311 |

|    | 10.6   | Commentary 3                                         |     |

|    |        | Strategic Direction 3                                | 312 |

|    |        |                                                      | 313 |

|    | 10.7   | For More Information                                 | 313 |

|    |        | Vendor Publications                                  | 314 |

|                       | Microprocessor Report Articles                  | 314 |

|-----------------------|-------------------------------------------------|-----|

|                       | Other Periodicals                               | 315 |

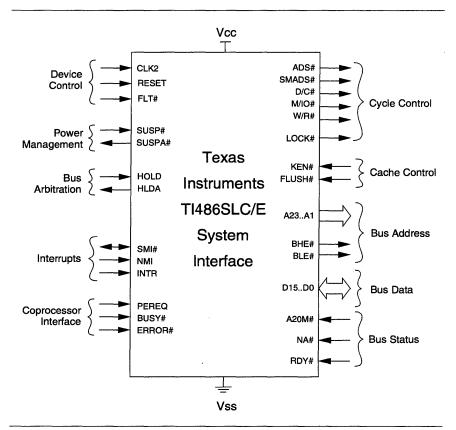

| 11 Texas              | Instruments 486 Microprocessors                 | 317 |

|                       | The TI486SLC/E and TI486SLC/E-V Microprocessors |     |

|                       | System Interface                                |     |

|                       | Compatibility                                   |     |

|                       | Vital Statistics                                |     |

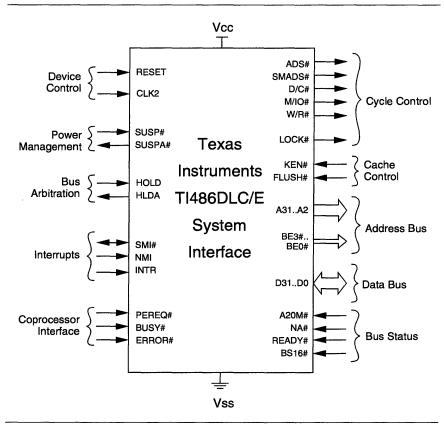

| 11.2                  | The TI486DLC/E and TI486DLC/E-V Microprocessors | 322 |

|                       | System Interface                                |     |

|                       | Vital Statistics                                | 323 |

| 11.3                  | The TI486SXLC and TI486SXLC2 Microprocessors    | 325 |

|                       | Clock Circuitry                                 |     |

|                       | Vital Statistics                                | 326 |

| 11.4                  | The TI486SXL and TI486SXL2 Microprocessors      | 327 |

|                       | Vital Statistics                                | 328 |

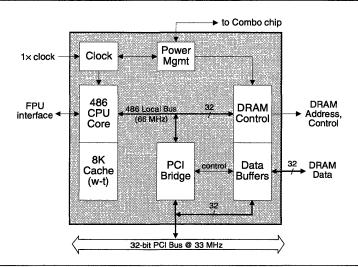

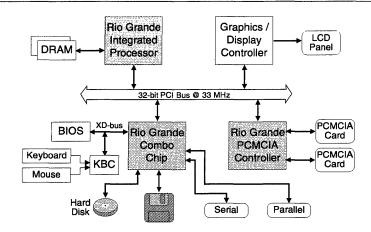

| 11.5                  | The TI "Rio Grande" Processor Chip Set          | 329 |

|                       | Support Logic                                   | 331 |

|                       | Vital Statistics                                | 332 |

| 11.6                  | Commentary                                      | 333 |

|                       | The i486SL Redux?                               | 334 |

| 11.7                  | For More Information                            | 335 |

|                       | Vendor Publications                             | 335 |

|                       | Microprocessor Report Articles                  | 335 |

|                       |                                                 |     |

| Part IV: Pentium-Clas | ss Processors                                   | 337 |

| 12 The In             | ntel Pentium Family                             | 220 |

| 12 IIICIII            | Overview                                        |     |

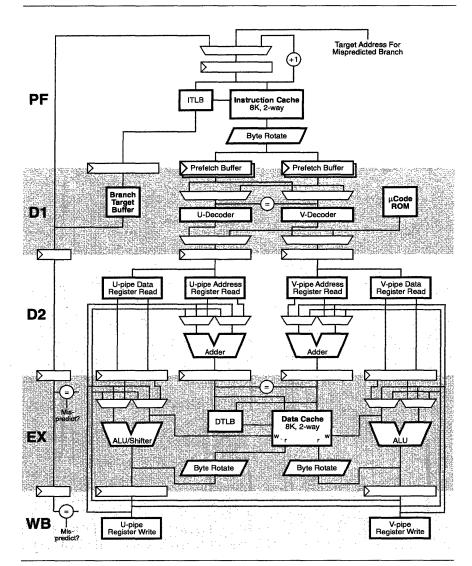

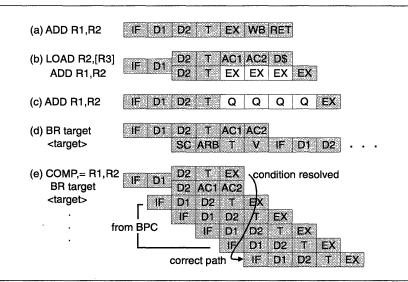

|                       | Pipeline Operation                              |     |

|                       | Instruction Issue Rules                         |     |

|                       | Instruction Cache and TLB                       |     |

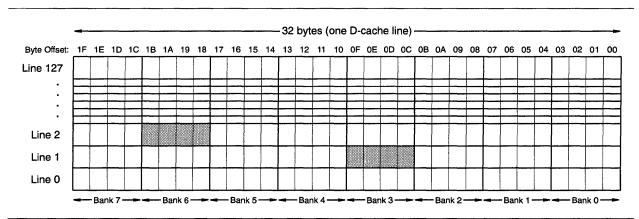

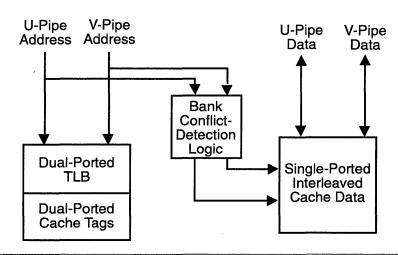

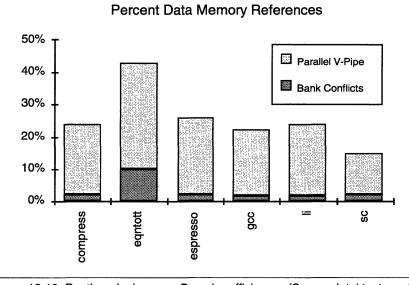

|                       | Data Cache and TLBs                             |     |

|                       | D-Cache Snooping                                |     |

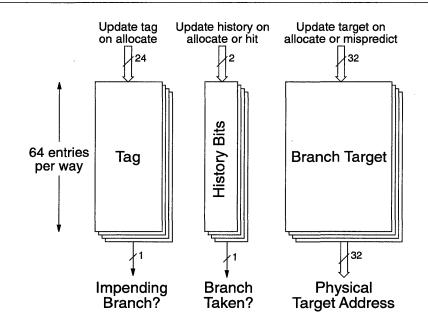

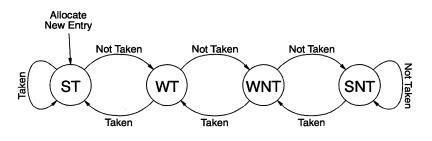

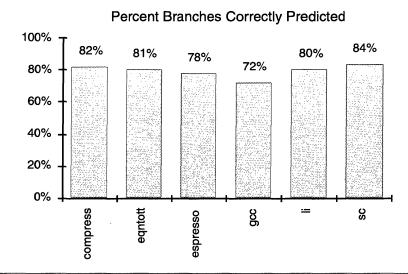

|                       | Branch Prediction Logic                         |     |

|                       | Floating-Point Unit                             |     |

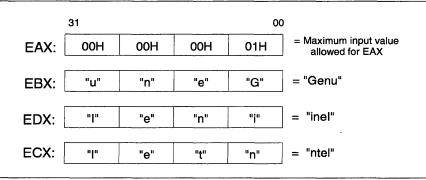

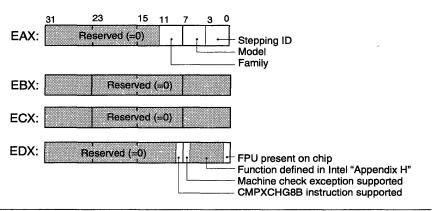

|                       | Architecture Extensions                         |     |

|                       | Software Optimization                           | 367 |

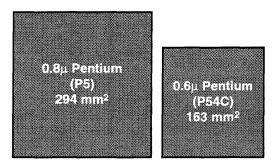

| 12.1                  | The Intel 0.8µ Pentium "P5"                     |     |

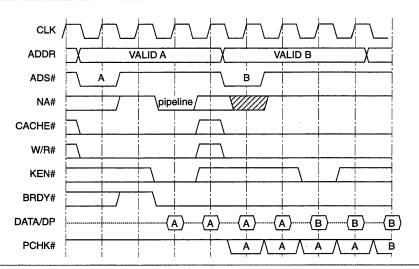

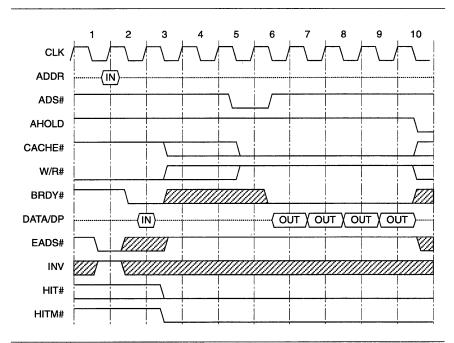

|                       | System Interface                                |     |

|                       | System Management Functions                     |     |

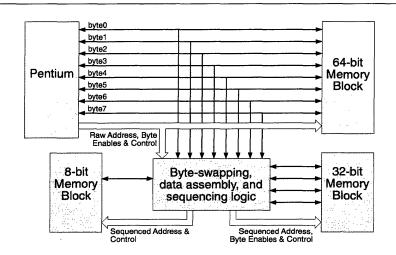

|                       | Bus Sizing                                      | 379 |

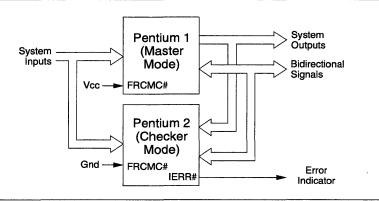

|                       | Functional Redundancy Checking                  | 380 |

|                       | Vital Statistics                                | 382 |

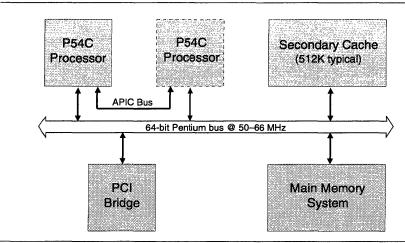

| 12.2                | The Intel 0.6µ Pentium "P54C"               | . 383 |

|---------------------|---------------------------------------------|-------|

|                     | Overview                                    | . 384 |

|                     | Bus Interface                               | . 386 |

|                     | Multiprocessor Support                      | . 387 |

|                     | Interrupt Control Logic                     | . 388 |

|                     | Clock-Generator Circuitry                   | . 389 |

|                     | Vital Statistics                            | . 389 |

| 12.3                | Futures                                     | . 390 |

|                     | The Intel "P24T"                            | . 390 |

| 12.4                | Commentary                                  | . 390 |

|                     | Competition with RISC                       | . 394 |

| 12.5                | For More Information                        | . 396 |

|                     | Vendor Publications                         | . 396 |

|                     | Microprocessor Report Articles              | . 396 |

|                     | Other Technical References                  | . 398 |

|                     | Other Periodicals                           | . 399 |

|                     |                                             |       |

|                     | en Microprocessors                          |       |

| 13.1                | F                                           |       |

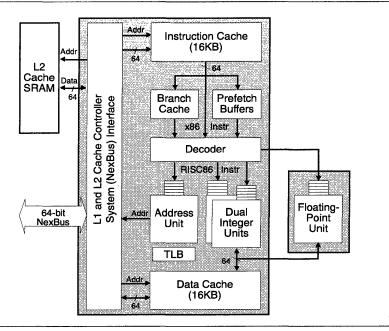

|                     | Core Design                                 |       |

|                     | Is it Superscalar Yet?                      |       |

|                     | Cache Logic                                 |       |

|                     | Execution Timing                            |       |

|                     | Branch Prediction                           |       |

|                     | Floating-Point Unit                         |       |

|                     | System Interface                            |       |

|                     | Performance                                 |       |

|                     | Vital Statistics                            |       |

| 13.2                | Commentary                                  |       |

| 13.3                | For More Information                        |       |

|                     | Vendor Publications                         |       |

|                     | Microprocessor Report Articles              | 415   |

|                     | Other Periodicals                           | . 416 |

| Volume II           |                                             |       |

| Part V: Perspective | ***************************************     | . 417 |

| •                   |                                             |       |

| 14 Core I           | Design and Implementation                   |       |

|                     | How Device Design Affects Product Selection |       |

|                     | Overview of Core Functional Differences     |       |

| 14.2                | Implementation Technology Alternatives      |       |

|                     | Complexity in the x86 Architecture          |       |

| 14.3                | Microprogrammed vs Pipelined Designs        |       |

|                     | Microprogramming Basics                     | 428   |

|    |       | Prelude to Pipelining – A Hardwired Machine       | 435 |

|----|-------|---------------------------------------------------|-----|

|    |       | Pipelining for Performance                        | 439 |

|    |       | Combining Microprogramming and Pipelining         | 444 |

|    | 14.4  | Pipeline Design Comparison                        | 446 |

|    |       | The Intel/AMD 486 Pipeline                        | 447 |

|    |       | The Cyrix/TI/IBM 486 Pipeline                     | 450 |

|    |       | The Intel Pentium Pipeline                        | 452 |

|    | 14.5  | Instruction Execution Timing Comparisons          | 454 |

|    |       | Register-to-Register ALU Operations               |     |

|    |       | Memory-to-Register Load Operations                | 456 |

|    |       | Memory-to-Register ALU Operations                 | 458 |

|    |       | Register-to-Memory ALU Operations                 | 459 |

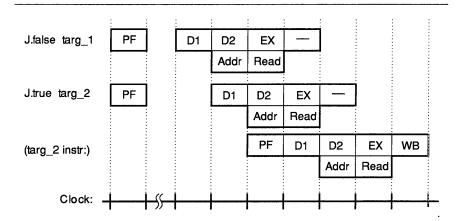

|    |       | Jump and Branch Operations                        |     |

|    |       | Integer Multiplication Operations                 | 468 |

|    | 14.6  |                                                   |     |

|    |       | Micro-performance Estimates                       |     |

|    | 14.7  | On-Chip Cache                                     |     |

|    |       | Cache Configuration                               |     |

|    |       | Cache Size                                        |     |

|    |       | Line Replacement Policies                         |     |

|    |       | External Cache Interface                          |     |

|    | 14.8  | Post-Pentium Implementations                      |     |

|    |       | Register Renaming                                 |     |

|    |       | Multiple Execution Units and Reservation Stations |     |

|    |       | Reorder Buffer                                    |     |

|    |       | Next-Generation Implementations                   |     |

|    | 14.9  | Device Design and Layout Comparison               |     |

|    |       | Intel i386DX Die Analysis.                        |     |

|    |       | AMD Am386SX/DX Die Analysis                       |     |

|    |       | Intel i486SX/DX Die Analysis (1.0μ)               |     |

|    |       | Intel i486DX/DX2 Die Analysis (0.8µ)              |     |

|    |       | IntelDX4 Die Analysis                             |     |

|    |       | AMD Am486SX/DX Die Analysis                       |     |

|    |       | Cyrix Cx486SLC/DLC Die Analysis                   |     |

|    |       | Pentium Die Analysis (0.8µ)                       |     |

|    |       | Pentium Die Analysis (0.6µ)                       |     |

|    |       | NexGen Nx586 Die Analysis                         |     |

|    | 14.10 | For More Information                              |     |

|    |       | Microprocessor Report Articles                    |     |

|    |       | Other Technical References                        |     |

|    |       |                                                   |     |

| 15 | Manuf | acturing Costs                                    | 509 |

|    |       | Manufacturing Cost: Theory                        |     |

|    |       | Waster and Die Coot                               | 510 |

|    |       | Manufacturing Defects and Die Yield             | . 512       |

|----|-------|-------------------------------------------------|-------------|

|    |       | Die Testing                                     | . 515       |

|    |       | Packaging                                       | . 516       |

|    |       | Final Test                                      | . 517       |

|    |       | Other Costs                                     | . 518       |

|    | 15.2  | Manufacturing Cost: Practice                    | . 523       |

|    |       | Process Technology Comparison                   | . 523       |

|    |       | Wafer Costs                                     | . 525       |

|    |       | Die Area and Net Yield                          | . 526       |

|    |       | Packaging Costs                                 | . 528       |

|    |       | Design Cost Comparison                          | . 529       |

|    | 15.3  | Manufacturing Cost: Summary                     | . 530       |

|    | 15.4  | Commentary                                      |             |

|    |       | Intel vs RISC Costs                             |             |

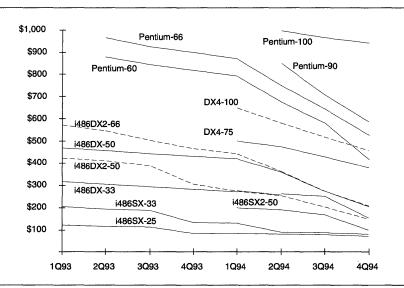

|    |       | Price vs Cost                                   | . 534       |

|    | 15.5  | For More Information                            | . 536       |

|    |       | Vendor Publications                             |             |

|    |       | Microprocessor Report Articles                  | . 536       |

|    |       | Other Technical References                      | . 536       |

|    |       |                                                 |             |

| 16 | Legal | Issues                                          | . 537       |

|    |       | Issues Affecting the x86 Business               | . 537       |

|    | 16.1  | Patents                                         | . 539       |

|    |       | Value of Patent Protection                      | . 539       |

|    |       | Criteria for a Patent                           | . 540       |

|    |       | Patent Infringement and Licensing               | . 542       |

|    | 16.2  | Copyrights                                      | . 544       |

|    |       | Software Copyright Protection                   | . 544       |

|    |       | Applying Software Copyrights to Microprocessors | 545         |

|    |       | Clean-Room Product Engineering                  | 546         |

|    | 16.3  | Trademarks                                      | . 549       |

|    | 16.4  | Trade Secrets                                   | . 550       |

|    | 16.5  | x86-Related Litigation                          | . 551       |

|    |       | Intel v. AMD                                    | . 554       |

|    |       | AMD v. Intel                                    | . 562       |

|    |       | Intel v. Cyrix                                  | . 563       |

|    |       | Intel v. ULSI System Technology                 | 567         |

|    |       | Intel v. Chips and Technologies                 | <b>56</b> 8 |

|    |       | Texas Instruments v. Cyrix.                     | 569         |

|    | 16.6  | Commentary                                      | . 571       |

|    | 16.7  | For More Information                            | 572         |

|    |       | Microprocessor Report Articles                  | 572         |

|    | _     |                                                 |             |

| 17 | Comp  | atibility Issues                                | 577         |

| 17.1 | Overview                                       | 578                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Degrees of Compatibility                       | 579                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Hardware Compatibility Challenges              | 580                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Software-Compatibility Challenges              | 581                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17.2 | Compatibility Assurance Methodologies          | 583                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | The Intel Approach                             | 583                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | The AMD Approach                               | 584                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | The C&T Approach                               | 584                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | The Cyrix Approach                             | 585                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | The TI Approach                                | 586                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | The IBM Approach                               | 586                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17.3 | Case Studies                                   | 587                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Pushing the Envelope of Market Acceptance      | 587                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Aftershocks                                    | 589                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17.4 | Commentary                                     | 592                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17.5 | For More Information                           | 593                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Vendor Publications                            | 593                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Microprocessor Report Articles                 | 593                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Other Periodicals                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 18.1 | •                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 18.2 |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Dispatch Capability                            | 603                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Caches and Memory Management                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Design Technology                              | 607                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Competing with Pentium                         | 608                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18.3 | Cyrix's M1                                     | 609                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Pipeline Design                                | <b>61</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | Register Renaming                              | 612                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| •    | Memory Bypassing                               | 612                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |